Other Parts Discussed in Thread: ALP

Hi Team,

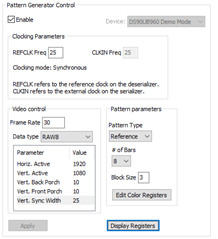

We are using ds90ub960-q1 to generate a test pattern refer to 7.5.12.4 of datesheet. We are not able to capture the test pattern. We see that the v4l2-ctl is select timeout and it is not getting any frame. The trace log shows that the LP sequence is error.

The relevant register configuration is as follows:

- CSI_PORT_SEL(0x32): 0x01

- FWD_CTL1(0x20): 0xF0

- CSI_PLL_CTL(0x1F): 0x02

- CSI_CTL1(0x33): 0x01

So what should be the values of cil_settletime and serdes_pix_clk_hz?