hello team,

Could you let me know the design considerations of 812s operates in RMII slave mode?

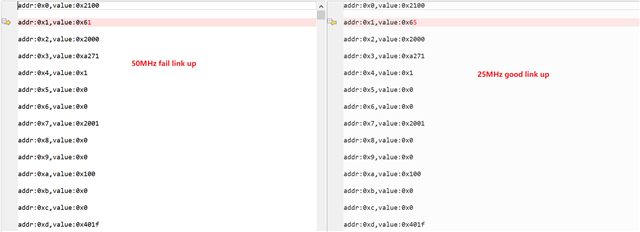

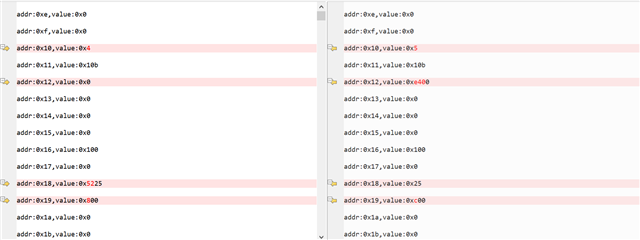

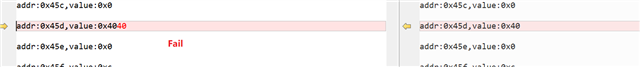

we fail to make it link up with the link partner when feeding XI with 50MHz reference clock from SOC/AM62, however, once we replace the reference clock with 25MHz crystal to XI&XO, we are able to get stable link up with link partner. Another odd thing is if XI=50MHz, clkout=50MHz instead of 25MHz according to datasheet description.

Reference clock is the only change which impact the link up.

- power up sequence checked with no abnormal: VDDX, RESET_N, Wake

- Strap pin checked for both hardware and register readback: RX_D1 pull up with 2.49kohm, other strap pin is float

- Disconnect SMI to avoid software conflicts

- Communication channel looks good as we have success link up with 25MHz crystal

- 50MHz reference clock duty cycle/rising/falling time is good, need additional time to test the clock ppm in the range of +-100ppm ( it comes from AM62A)

Need you support to give some guidance on this case.

Regards

Dongbao