Part Number: DS90UB960-Q1

We are using PatGen mode of ds90ub960 to generate (1280*720, RAW8) fake data to CSI-2 port 0 and NVIDIA Orin was used to read the CSI-2 data.

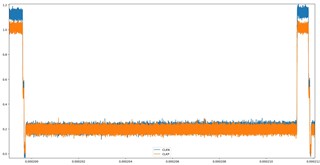

We have probed the CSI0_D3P and CSI0_D3N pins but both the voltage level range and waveform are odd.

Figures below shows the waveform from Oscilloscope:

Question:

1) We noticed the signal voltage level is range from 0-500mV during HS transmit. That is not the typical value(200mV) and even over the MAX(250mV) range which recommended in the MIPI D-PHY handbook. Will the output voltage can be a problem for Orin to read the data?

2) The voltage level of the signal in HS mode is not fixed, which is changed from 150mV to 500mv(From the figure, it includes several completely different waveforms in HS mode). Is it normal? If normal, does each segment of the waveform represent a different meaning?