Other Parts Discussed in Thread: DS90UB953-Q1

Dear team,

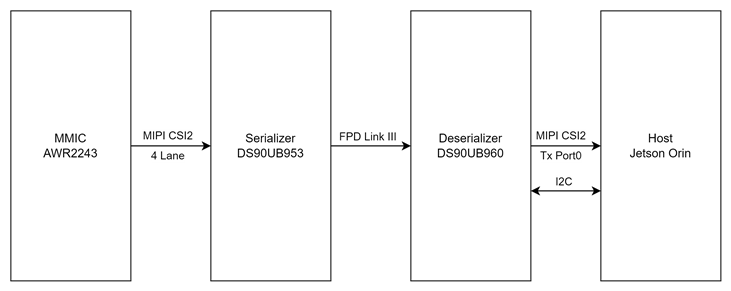

We are using DS90UB953-Q1 and DS90UB960-Q1 as SerDes to transmit the video stream from a sensor with MIPI CSI-2 interface. We only connect one sensor and set the strean output to DS90UB960 CSI2 port0.

However, we cannot read the video stream from the termination side and we got “LP sequence Error” from termination's D-PHY.

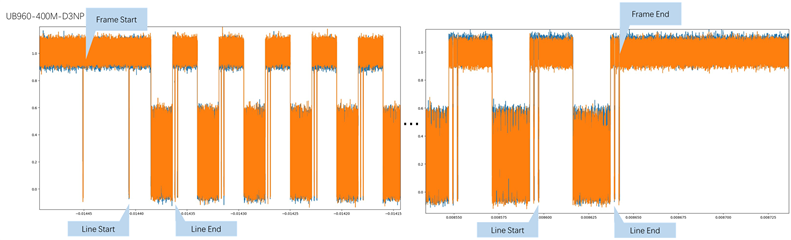

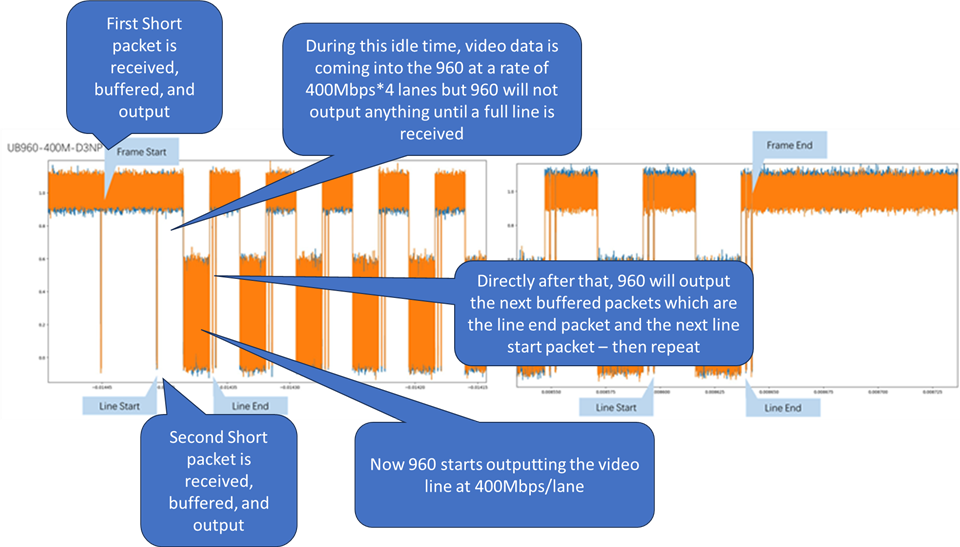

We probed the waveform on the lanes between the sensor and Orin, we found that the time specifications in the long and short packets of CSI-2 are consistent with the requirements in the CSI2 manual. However, compared to the CSI2 waveform sent by the sensor, the timing of the frame and line sync packets from 960 CSI2 output port appears to have shifted.

The frame end packet did not appear at the end of the frame data transmission, but appear at the place where very close to the start of the next frame. And the line start/end packet also seems strange.

There is always a long LP status hold after the line start packet is sent, before the line data. However, the line end packet will appear as soon as the line data has finished.

The sync packets in the waveform of the sensor CSI2 output port are correct, but become strange after SerDes in the DS90UB960 output, which confused us.

I think something must have gone wrong when processing the SerDes, however we haven't found any errors according to the registers both in SerDes.

Could you please give us an idea of how to overcome the above problem?

Thanks a lot,

Lee