Part Number: TLK6002

Other Parts Discussed in Thread: CDCM6208

Hi

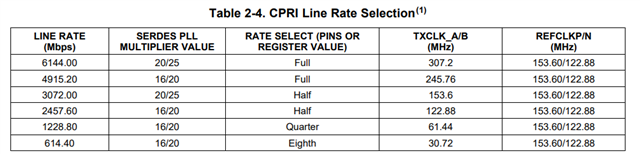

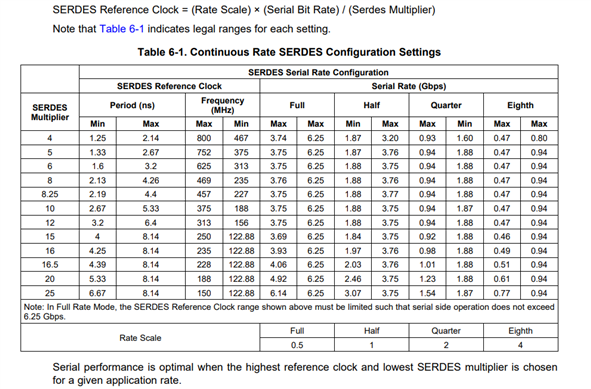

I am trying to configure TLK6002 in Half-rate mode. I am following the below table to select reference clock and SERDES Multiplier.

I am configuring Serdes to work at 2.46 Gbps at HALF_RATE mode. Based on the formula provided below and sedres multiplier value from the table I have choosen the following configuration.

1.SERIAL RATE : 2.46Gbps.

2. Serdes MULTIPLIERr: 20

3. TX_CLK= ( serdes_serial_rate/20 ) = 123Mhz;

4. from the below formula I got REF_CLK =123 Mhz;

When I program the above configuration I am getting Transmit Overflow and Underflow errors.

Is there any corrections to be made in Calculations ?

Note: I have programmed the 0x01 register to Half rate.

Thanks

Mallikarjuna B