Other Parts Discussed in Thread: TCA9509

Hi,

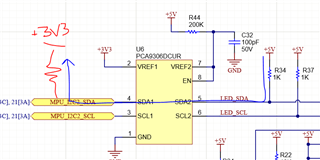

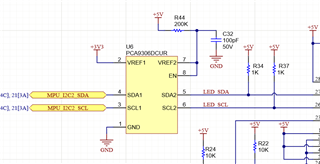

using the PCA9306 in a design and I would like to know if there can be a backfeed current issue through the SDA/SCL pins.

In this design, +5V rises first, and +3V3 follows a few milliseconds later. I understand there will be some leakage from VREF2 to VREF1, limited by the 200K. But what about leakage from the SDA and SCL signals? Can there be leakage current from SDA2 to SDA1, or from SCL2 to SCL2 from the 5V pull-up resistors?

Thank you