Part Number: DS90UB928Q-Q1

SI simulation engineer states that the only way to reduce insertion losses is to reduce the length trace from Connector to RIN+-, and use a different ESD Protection diode.

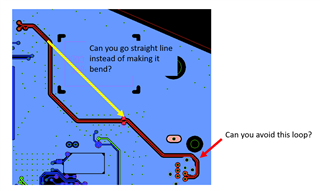

Currently we reduced from 80mm to 63mm but we still seeing the problem, could you recommend any other advice to improve?