Other Parts Discussed in Thread: DP83869

DP83869HM: 100M Media Converter no traffic on or above Layer 2 Ethernet

Dear Sir,

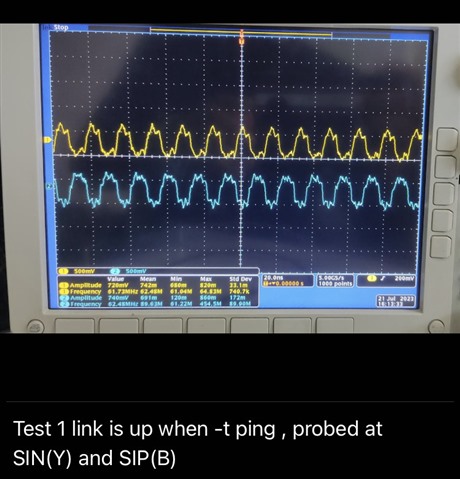

We are using DP83869HM as a 100M media converter with the following topology:

PC_A <--- copper --> DP83869 board #1 <---> transmission medium eg. fiber <---> DP83869 board #2 <-- copper --> PC_B

We have successful auto negotiation and stable link up. All registers show base page/code word sent and received with no problem.

Based on the above topology, we have successful layer 1 Ethernet communication.

However, any traffic type between the two PC's belonging to layer 2 Ethernet (and above) will not pass.

PC_A and PC_B happen to be on the same subnet, ARP requests are sent by each PC with no response. Ping test returns "destination host unreachable" meaning there is no route to destination to begin with.

To rule out any PC setup issue, when connecting PC A and B directly, ARP requests are answered by each machine and ping test is successful. This means the problem is not within PC_A or PC_B but with the DP board.

We have even tried to increase the inter packet gap of each NIC on each PC, as well as turning off Energy Efficient Ethernet. Again, link was up and stable; but still, there was no traffic on layer 2 Ethernet and above.

We tried everything with no luck.

We then decided to have a deeper look into certain registers, hoping to find something unusual to use it as a lead. Most registers readings looked normal, except:

- Register 13h (bit [2]) showing a flag for Overflow/Underflow. The datasheet stated that this error explained in CDDS document #475 which we cannot find. The datasheet also stated that in this case of error it is recommended not to turn on DS, we have no idea what DS stands for.

- We have also noticed that register 4F shows no sync, but we believe that this register may not be of concern for 100M media converter mode.

- Register 10h bit [11] value is 1 instead of 0.

We are not sure but we think the problem is within the Tx or Rx FIFO's size of the copper side but don’t know what to do.

We seek your assistance..

Below are stable readings of selected registers for your kind review:

|

0x0 |

3100 |

|

0x1 |

796D |

|

0x2 |

2000 |

|

0x3 |

A0F1 |

|

0x4 |

0181 |

|

0x5 |

CDE1 |

|

0x6 |

006D |

|

0x7 |

2001 |

|

0x8 |

4006 |

|

0x9 |

0000 |

|

0xA |

0800 |

|

0xD |

401F |

|

0xE |

0000 |

|

0xF |

F000 |

|

0X10 |

5848 |

|

0X11 |

First 7F02 Next 6F02 |

|

0X12 |

0000 |

|

0X13 |

First 1C44 NEXT 0004 |

|

0X14 |

29C7 |

|

0X15 |

0000 |

|

0X16 |

0000 |

|

0X17 |

0040 |

|

0X18 |

6150 |

|

0X19 |

4004 |

|

0X1A |

0002 |

|

0X1E |

0012 |

|

0X1F |

0000 |

|

0XC00 |

2100 |

|

0XC01 |

614D |

|

0XC02 |

2000 |

|

0XC03 |

A0F1 |

|

0XC04 |

0020 |

|

0XC05 |

0000 |

|

0XC06 |

0000 |

|

0XC07 |

2001 |

|

0XC08 |

0000 |

|

0X6E |

0A0C |

|

0x1DF |

0045 |

|

0x01EC |

1FFD |

|

0x4F |

0200 |

|

0x2D |

0000 |

|

0xC10 |

3148 |

|

0x0032 |

0050 |

|

0x006F |

0000 |

|

0x0C19 |

First 0010 next 0000 |

|

0x0C18 |

01FF |

|

0x002E |

0221 |

Looking forward to your kind assistance,

Regards,

Sandeep