Hi PHY Team Experts,

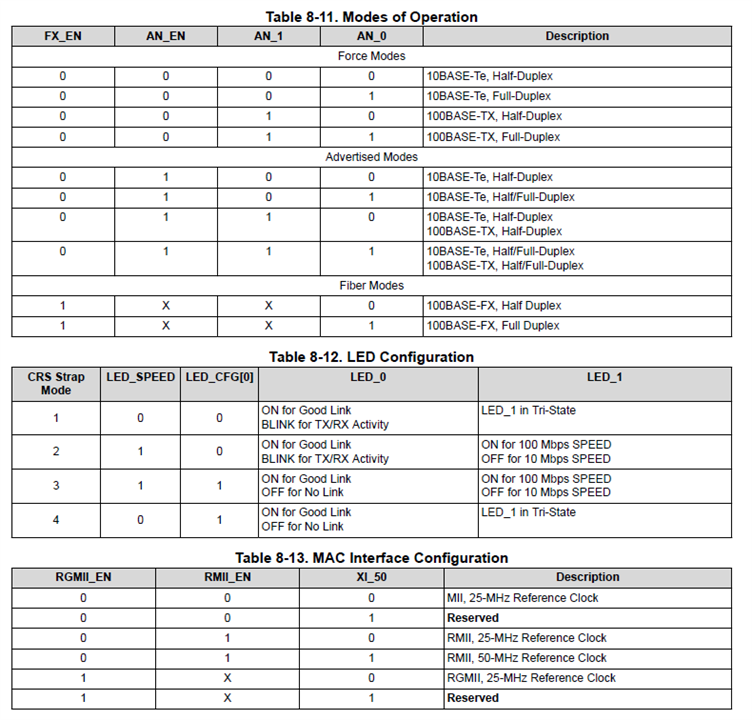

Customer is using RMII interface(MCU_CPSW0) to connect with an external TI PHY (DP83822). The link is up, but it cannot ping PC.

We have provided information in details and tracking in the below thread with our SOC expert.

At the same time, we may need your help to check if the internal delay values being used and the properties being set are correct and will work with 100mbps full duplex link.

+ mcu_phy2: ethernet-phy@2 {

+ reg = <2>;

+ rx-internal-delay-ps = <1>;

+ tx-internal-delay-ps = <1>;

+ };

+};

Kind Regards,

Kevin