Part Number: DP83822IF

Hi TI,

We have board based on DP83822.

Schematic same as the EVM -- no Bootstraping resistors (configured by MDIO)

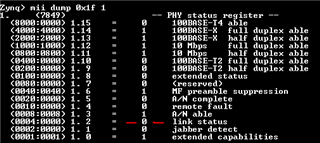

We have link to PC and have cominucation with SMI with the chip

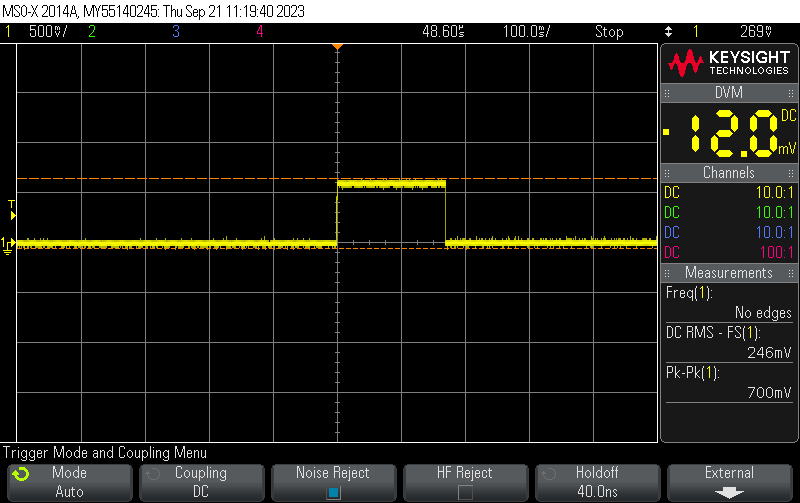

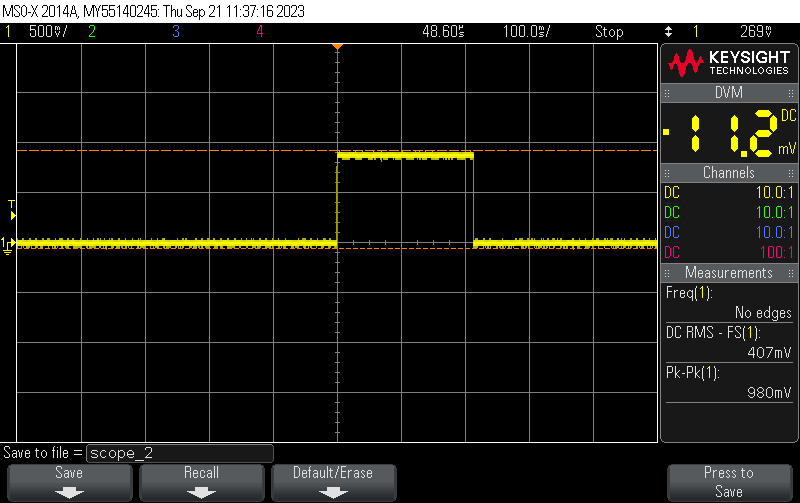

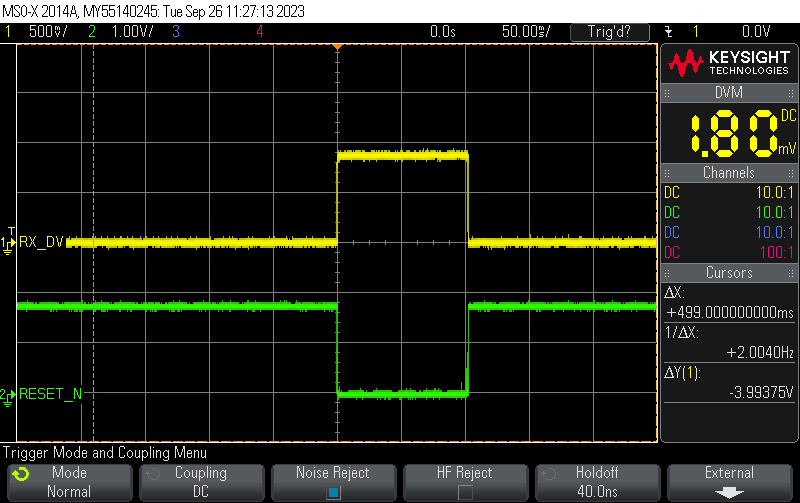

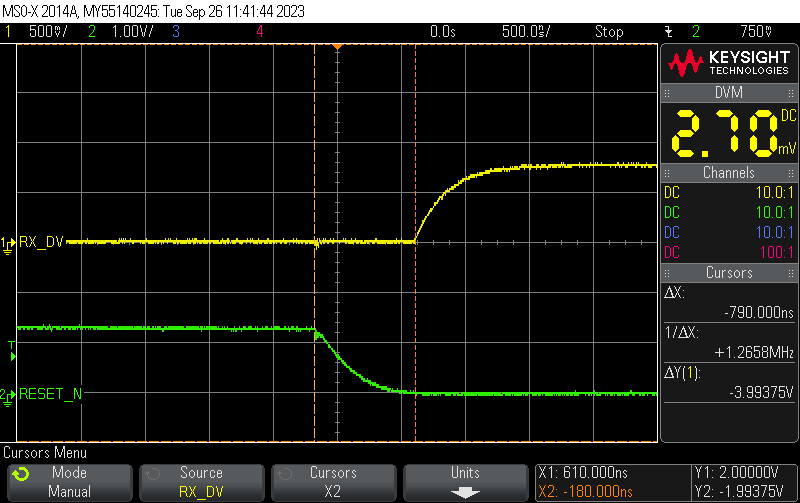

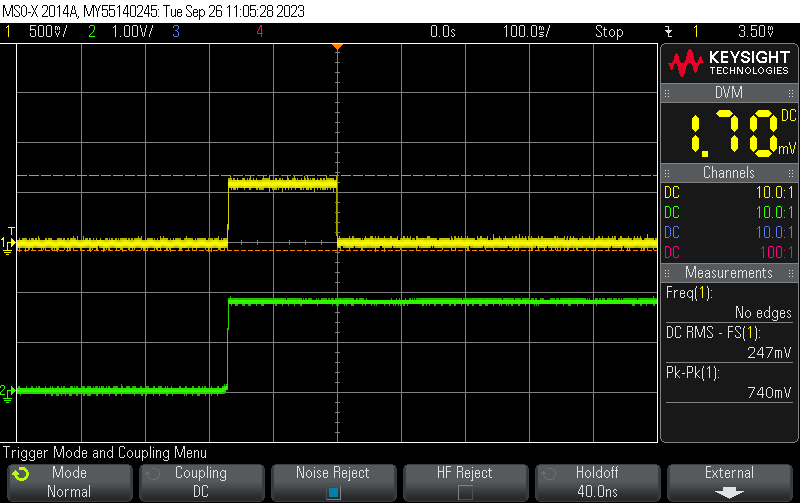

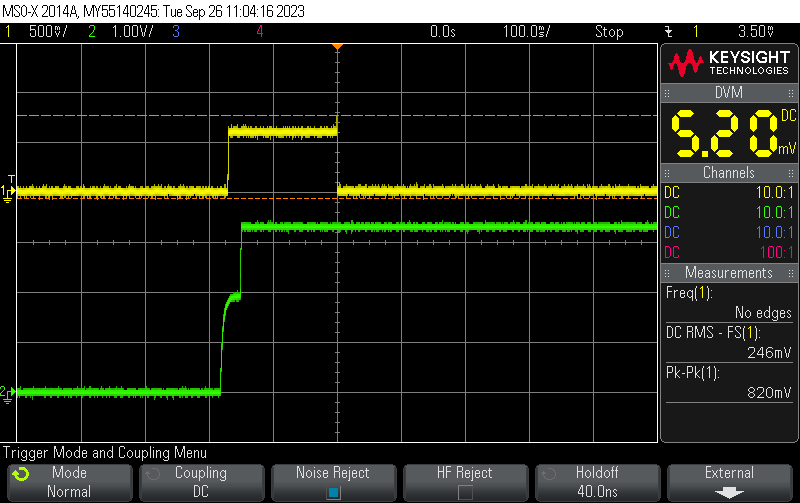

We encouter with problem in RGMII side

When we connect RX_DV line to MAC side (ZYNQ 7000) and power on the chip have no link

We disconnect the line and we have the link back

What can be the problem ?

Thanks in advance