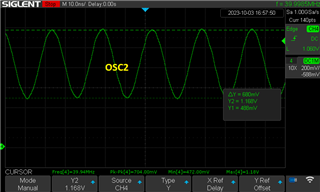

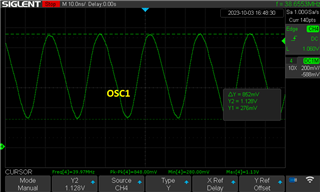

Debugging an issue with only some registers accessible and stumbled on his thread. Our crystal voltage too is between 0.25V and 1.2V, at least as measured with a passive probe, so it's likely adding some capacitance during measurements. We did not include series resistor placeholder in the design, and it is not practical to add it at this stage as the layout is pretty tight. What can be done with tweaking load capacitance and how does one go about that? Seems I'd start pulling the clock value away from the target.

Any suggestions are greatly appreciated!

Attached are our schematic and the plots of OSC1 and OSC2