Other Parts Discussed in Thread: DS90UB948-Q1,

Hi,

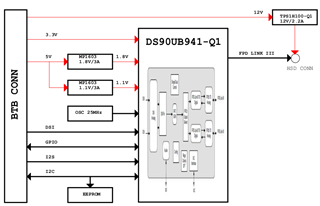

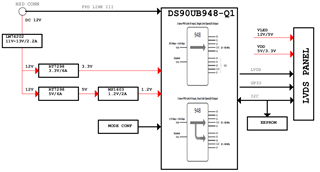

I successfully connect DS90UB941AS-Q1 with DS90UB948-Q1.

The DS90UB948-Q1 have a i2c touch for lvds panel.

But the i2c touch is quite lagging.

Here is the video:

Our Native i2c touch expect behavior like this: