Part Number: DP83TD510E

I am having problems using DP83TD510E.

Environment:

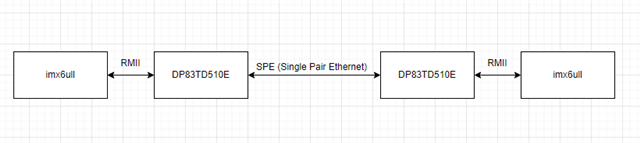

DP83TD510E works in rmii slave mode. Soc provides a 50Mhz clock to the xi pod.

CRS_DV/RX_DV Pin 18 is configured as CRS_DV (default).

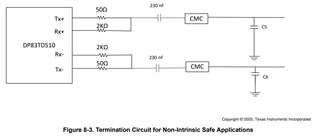

Receiver with tapping at 50 Ω (Recommended).

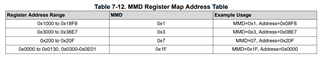

The id of the phy chip is set to 0.

linux system from the following github link.

https://github.com/nxp-imx/linux-imx/blob/lf-6.1.y/drivers/net/phy/dp83td510.c

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet1>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

phy-reset-gpios = <&gpio1 1 GPIO_ACTIVE_LOW>;

phy-reset-duration = <2>;

status = "okay";

};

&fec2 {

......

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@0 {

compatible = "ethernet-phy-id2000.0180";

reg = <0>;

clocks = <&clks IMX6UL_CLK_ENET_REF>;

clock-names = "rmii-ref";

};

......

};

};

......

pinctrl_enet1: enet1grp {

fsl,pins = <

MX6UL_PAD_ENET1_RX_EN__ENET1_RX_EN 0x1b0b0

MX6UL_PAD_ENET1_RX_ER__ENET1_RX_ER 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA0__ENET1_RDATA00 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA1__ENET1_RDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_EN__ENET1_TX_EN 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA0__ENET1_TDATA00 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA1__ENET1_TDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_CLK__ENET1_REF_CLK1 0x4001b039

MX6UL_PAD_GPIO1_IO01__GPIO1_IO01 0xb0

>;

};

......

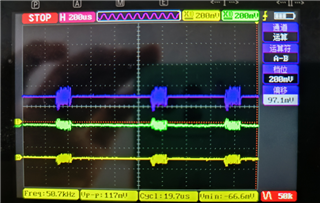

The DP83TD510E is always in the Link is down state, and I don't know how to deal with it. The DP83TD510E has been registered.

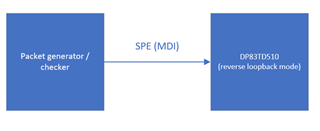

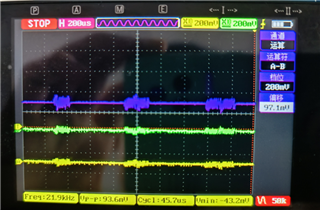

I tried to test Loopback Modes, but I still don't know how to handle it.