Other Parts Discussed in Thread: TCAN4550, RM46L852,

Dear Team,

We've got an issue related to high temperature. The situation of the failure and the TCAN4550 settings are as follows:

[Issue]

Multiple errors occurred at high temperatures (about 60 degrees), resulting in a reported CAN communication failure. The failure rate is approximately 5%.

Upon checking the Interrupt register (h1050), bits 23, 24, and 25 are set.

Upon checking the Protocol status register (h1044), bits 5, 6, and 7 (Error Warning, Error Passive, Bus Off) are found to be triggered.

[The circuit structure and TCAN4550 settings are as follows]

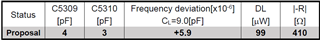

TCAN4550 Bit timing setting : (@40MHz crystal +-10ppm tolerance / Fixed 500kbps )

BRP = 10 - 1; / SJW = 1 - 1; TSEG1 = 6 - 1; TSEG2 = 1 - 1;

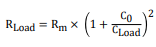

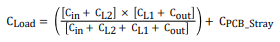

and we've checked the load capacitor value according to the crystal evaluation report with our PCB board.

[Questions]

1. Even when I changed the setting from 10TQ to 80TQ for testing, the defect phenomenon remained the same. Do I need to align the bit setting timing of RM46L852 as well?

-

brp = 1- 1; / sjw = 10 - 1;/ tseg1 = 69 - 1;/ tseg2 = 10 - 1;

-

As you can see in the block diagram above, the connection between the two boards is not a long CAN cable but a trace of approximately 250mm. If you have any recommended settings for a bit rate of 500kbps at a low speed, please suggest them.

-

If there are any other improvement suggestions besides changing the bit time, please let me know.