Part Number: DP83822I

Hi team,

I have a question about the clock interface requirement in the EtherCAT application.

In another e2e:

The clock requirement of the EtherCAT application is explained as 25 ppm.

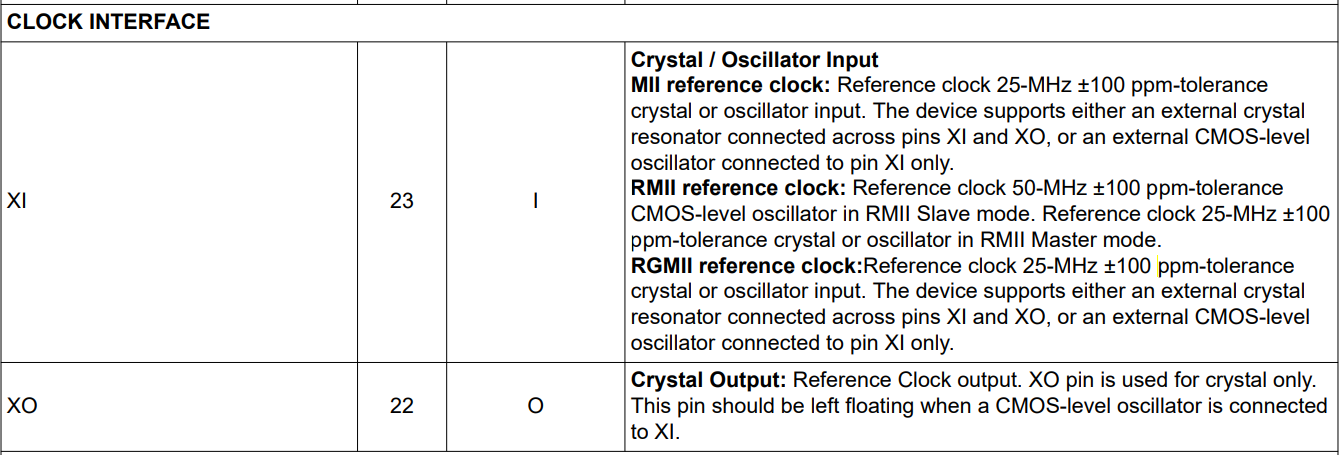

And in the datasheet of our DP83822, the clock interface requirement is explained as 100 ppm.

Thus, the question I want to ask is:

1. Is the clock interface requirement more strict in the EtherCAT application? And it must be 25ppm?

Thanks and best regards,

Matt.