Part Number: DP83867IR

Hi,

We are using the part DP83867IRRGZ in our board.

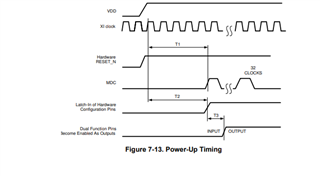

We observed that the Crystal connected (ABM8G-25.000MHZ) to the PHY is not providing the clock input.

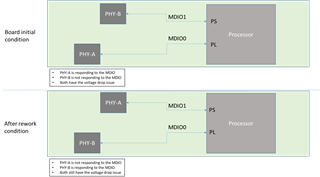

We tried programming the MDIO and observed that the PHY is also not responding. Checked the PHY reset input, PHY is out of reset.

Can you please help with possible causes for the issue?

Thanks & Regards,

Nanjunda M