Other Parts Discussed in Thread: TS3DV642

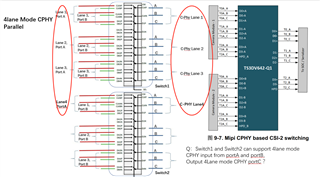

When I use TS3DV642 as a MIPI CHY mux with MAX96712,I have a problem- that the Ti mux just support 3lane mode CPY, but max96712 is 4lane CPHY,please see the figure below:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

When I use TS3DV642 as a MIPI CHY mux with MAX96712,I have a problem- that the Ti mux just support 3lane mode CPY, but max96712 is 4lane CPHY,please see the figure below:

Hello,

I am looking at your response and will response shortly.

Thanks,

Zach

Hey,

I'm not fully sure I understand, but it seems you are looking to use channel A and B at the same time. To compensate for the lack of lanes. This is not possible.

Please correct me if my interpretation is incorrect.

hi Vishesh,

Thanks so much for your answer,

please see the figure, my problem is if the two muxs can be used in parallel so that can support 4lane CPHY(you can see the mux, channel A and B both just support 3 lane CPHY, but we must use 4lane CPHY).

Kai Cheng

hi Zach,

Thanks so much for your answer,

please see the figure, my problem is if the two muxs can be used in parallel so that can support 4lane CPHY(you can see the mux, channel A and B both just support 3 lane CPHY, but we must use 4lane CPHY).

I have no experience to use the two muxs in parallel at the same time, would you please help research it?

Kai Cheng

Hello, Cheng,

Yes, I am assuming that all the switches will be TS3DV642. Depending on data rates and loss profile after the output of the final mux I would recommend the DPHY440SS MIPI retimer as well to compensate for additional insertion loss of each mux. What is the application? Please see this E2E thread https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1191596/ts3dv520-cascading-4-channel-csi-from-four-inputs-to-one-output-using-three-2-1-multiplexers.

thanks,that means if we can control the total trace insert loss and impedance,if I use additional MIPI timer,the two mux used in paralle will be OK?

Another question is this is used in Auto driving domain,so can you find a 125℃ auto car level component,and support MIPI CPHY retimer?

how do you consider the risk,and how can I evaluate the insert loss and other SI parameters?

kai

Hello, Kai,

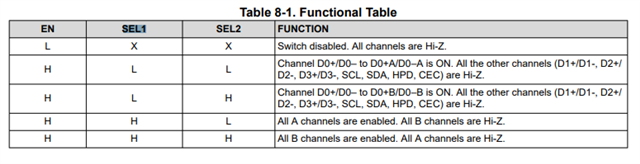

I now understand that you want to break up the 4 lanes by putting 1 lane onto a separate MUX. The part to part skew for this part is not given in the datasheet and per the specification your inter-pair skew must be within +/-3.5 UI. If you break up the lanes, there is no way to guarantee that you can meet this requirement.

Also, unfortunately we do not have an automotive grade MIPI retimer solution.

Thanks,

Zach