Other Parts Discussed in Thread: DS250DF210, , DS280DF810, DS250DF230

Hello,

I was not able to find an answer to a question that I have neither in the datasheet nor the programming guide.

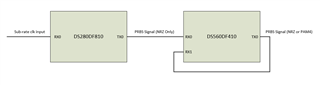

Here is a basic diagram of the circuit in question:

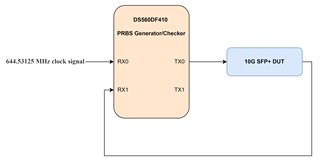

In this thread TI answers that the DS250DF210 can be configured to generate a 10.3125 Gbps PRBS output using a 644.53125 Mhz clock source at its input because the retimer can achieve a lock using input data rates that are divided by 2,4, 8, and 16.

Is this also the case for the DS560DF410? What are the limits of the retimer locking, are they also 2, 4, 8, and 16?

Kind regards