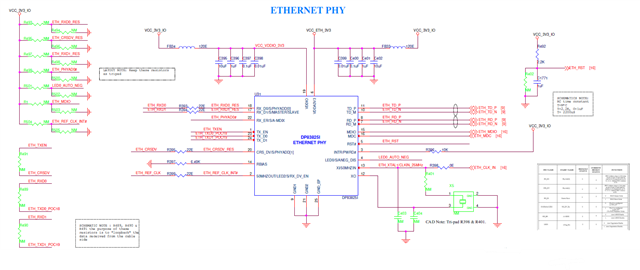

Other Parts Discussed in Thread: DP83825EVM

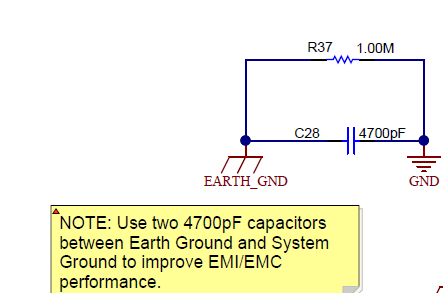

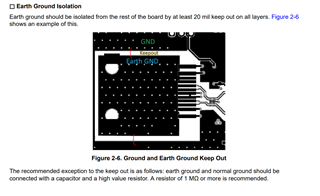

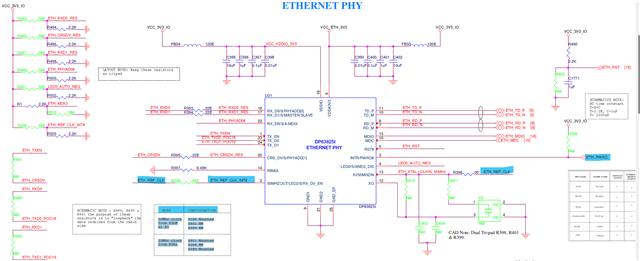

- In the evk of DP83825IRMQR, its recommended to use 2 4700pf caps. Not able to understand single 4700pf with 1M cap can itself help EMI. Why 2 are recommended?

- Also, how this network is helping to improve EMI.

- Share the EVK BOM.

- attaching image below