Part Number: DP83825I

Other Parts Discussed in Thread: SK-AM62,

Hello Experts,

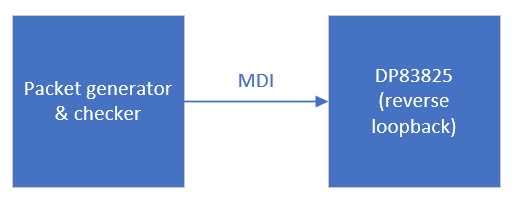

We have designed EPHY circuit with DP83825IRMQR on our PCB.

But, when Ethernet cable connects from this PCB to PC for the test, link up can be done (100Mbps, Full-duplex) but ping cannot succeed.

Parts name of PHY and MCU are the followings.

PHY: DP83825IRMQR x2 (eth0, eth1) used as RMII master mode

MCU: AM6231ASGGGAALW

We have designed the MCU firmware of Ethernet communication module based on the one for SK-AM62.

(Changed only some parameters and defines from for RGMII mode to for RMII mode.)

We have already confirmed that the port mode select of both eth0/eth1 on MCU is RMII.

Details of ping NG;

PC --> PCB: PC send ARP request to PCB(as global packet), but PCB send no response message to PC.

PCB --> PC: PCB send ARP request to PC(as global packet), then PC send the response message to PCB, but then PCB send ARP request to PC(as global packet) again. It repeats until ping command of PCB is stopped.

I had asked about this issue to MCU experts on the following thread.

This new thread is to ask about it to EPHY experts followed by the advice of MCU experts.

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1269687/am623-cannot-establish-ethernet-rmii-data-communication-tx-rx-between-mac-and-phy/4833929#4833929

The attached PDF file is the Ethernet circuit between MCU and PHY and around PHY from the circuits of our PCB.

Please review it, and please give us some advice if it can be guessed something suspicious by the above information, or if there are what we need to check more.

Thanks,

Yasuhiro Nakashima

EthernetCircuit20230914.pdf