Part Number: TL16C750E

Hi Expert,

My customer have a problem when testing the TL16C750E, please refer below.

1. No problem transmitting data

2. There is an abnormality in receiving data. The main problem is that it may be messed after receiving 0xFF.

- For example, after receiving 01 02 03 FF 04 05, only 01 02 03 FF 05 is left when reading it out, and the 04 after FF will disappear.

- If the received data ends in FF, even stranger phenomena may occur.

- For example, after disabling the FIFO (the default value of FIFO is disable after power-on), send a FF to it, and the FF can be read. After that, no other data will be sent, and then it will be judged whether there is data. LSR will always get the flag with data, and then when reading data, it will keep sending the data in the FIFO repeatedly in a loop.

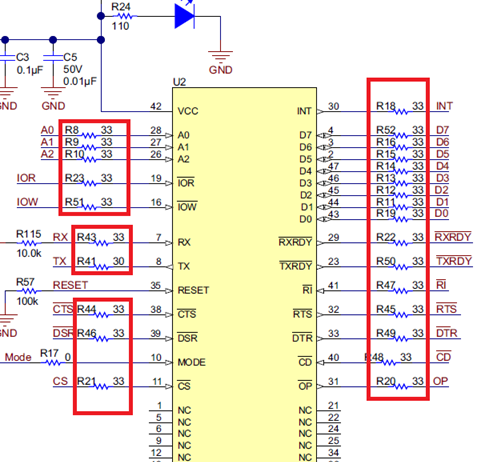

Inaddition, it can be found in the EVM board manual that all data buses will have a 33 ohm resistor in series. Is this for current limiting or EMI suppression? Is this a must?

Thank you.

Darren