Part Number: DP83TG720S-Q1

Hi team,

Here is a question one of our customers is experiencing, could you please provide some troubleshooting suggestions?

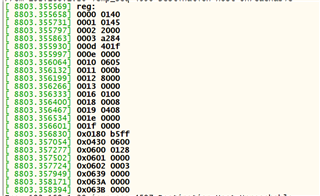

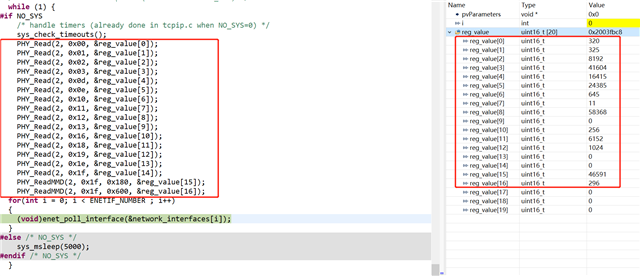

When debugging DP83TG720S-Q1, I configured the PHY to RGMII mode and completed the initialization sequence. After the initialization is completed, the relevant registers are dumped, and the working mode and Link Up status of the PHY chip are confirmed:

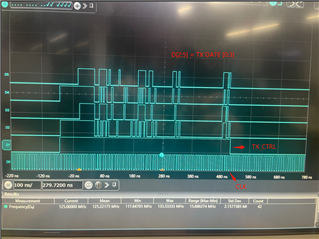

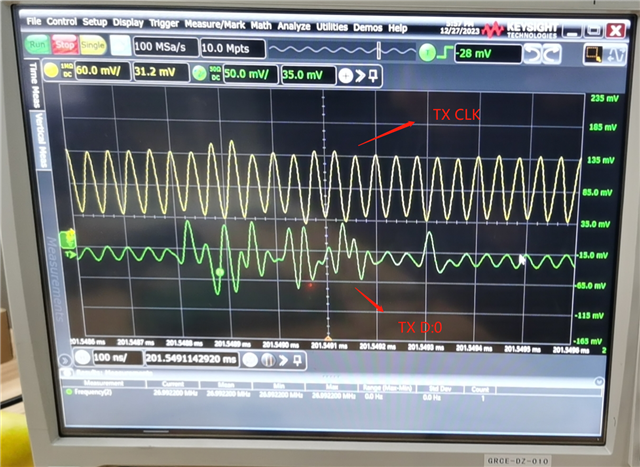

But when I communicated through RGMII, it's failed. I guess it's the timing of RGMII. I caught the waveform of RGMII through the oscilloscope, but I couldn't analyze it.

I want to confirm whether it is a RGMII timing problem? If it is the RGMII timing, how can I adjust it?

This user says the signal voltage amplitude is correct and the picture above shows incorrect is an oscilloscope setting issue.

Best Regards,

Amy