Part Number: SN65DSI83

what's the LVDS output clock (pin "A_CLKN", "A_CLKP") cycle to cycle jitter? seems not to list in the datasheet, please help provide the cycle to cycle jitter, thanks!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN65DSI83

what's the LVDS output clock (pin "A_CLKN", "A_CLKP") cycle to cycle jitter? seems not to list in the datasheet, please help provide the cycle to cycle jitter, thanks!

Hi Vishesh,

The reason why we need LVDS clk cycle to cycle jitter is to calculate LVDS timing. From snla249.pdf, need RSKM > = cable skew + CLK cycle to cycle jitter + ISI, so do you know how to get clk cycle to cycle jitter?

Thanks

Wenjun

Hey Wenjun,

This is the proper procedure to measure cycle to cycle jitter. However this may be too tedious to do without an automated script.

We unfortunately cannot run this test on our end as this is a legacy product and don't have a script designed to run it.

Hi Vishesh,

Thanks for the test procedure. As the project is still under planning phase, so we cannot measure cycle to cycle jitter directly now, and we are evaluating the LVDS timing by simulation and calculation. In my opinion, cycle to cycle jitter at receiver is transmitter cycle to cycle jitter combined with PCB/cable's impact, this is why I request the transmitter SN65DSI83 cycle to cycle jitter, or can we think SN65DSI83 cycle to cycle jitter is zero?

thanks

wenjun

Hey Wenjun,

Like I mentioned we unfortunately do not have that data and I don't have the means to measure that.

Regarding the cycle to cycle jitter, a workaround may be to use REFCLK and use the cycle to cycle jitter for whatever device you are using as REFCLK as the cycle to cycle jitter of the LVDS clock.

Hi Vishesh,

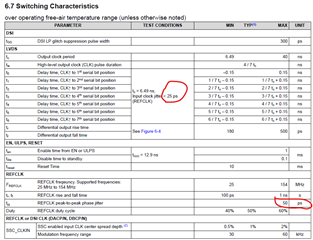

Ok, thanks, and SN65DSI83 datasheet lists 25ps RefCLK jitter, so can I use it as LVDS CLK cycle to cycle jitter?

thanks

wenjun

Hey Wenjun,

This measurement is the phase jitter of the clock not the cycle to cycle jitter.

Hi Vishesh,

One more question hope to discuss with you. as you mentioned we can use REFCLK cycle to cycle jitter as workaround for LVDS CLK cycle to cycle jitter.

SN65DSI83 provide REFCLK phase jitter, max 50ps (as figure1). according to the relationship between cycle to cycle jitter and phase jitter, as figure2, the max REFCLK cycle to cycle jitter should be 200ps (??), so we can use max 200ps as LVDS CLK cycle to cycle jitter for workaround, right? thanks a lot.

figure1

figure2

Hey Wenjun,

Unfortunately its not that simple.

Here is a document which explains how all three are related.

Clock (CLK) Jitter and Phase Noise Conversion | Analog Devices

Hi Vishesh,

Thanks a lot for the reply and patience! and two question on the jitter

1. as cycle to cycle jitter is to do second derivation for phase jitter, so cycle to cycle jitter pk-pk value is less than phase jitter pk-pk value, and need know phase jitter function to generate cycle to cycle jitter. But now we don't have this phase jitter function, can we use phase jitter pk-pk value (50ps or 25ps) as cycle to cycle jitter? Or other workaround?

2.just want to confirm: is below t0~6 relative with the present CLK rising edge or the last cycle clk rising edge?

thanks

wenjun

cycle to cycle is best at comparing adjacent clock cycles but isn't good at determining a pattern between non-adjacent clock cycles. Phase and period jitter are better at standardizing clock frequency. If you use the phase jitter as the cycle to cycle jitter this application should work, as it is more stringent.

I'm not sure what your asking here, but as based off of the image, the reds are triggered by the red clock edge, and the blue is triggered by the blue clock edge.

Hi Vishesh,

Hope to consult you for one more question: as LVDS CLK cycle to cycle jitter is not available now, the workaround is to use REFCLK phase jitter as an alternative, then should we use 25ps or 50ps phase jitter more reasonable as below datasheet table? Maybe 50ps is too pessimistic as cycle to cycle jitter is much smaller than phase jitter, so what's your opinion?

thanks

wenjun

If you are looking to calculate the jitter for the LVDS side, I would say using the 25ps will be the closer approximation.