Part Number: DS280DF810

Other Parts Discussed in Thread: DS280MB810

Hi

We have question about register settings of DS280DF810 below,

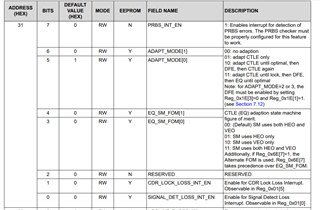

According to the Programmer's Guide of DS280DF810, we can see 7.43 Adjustable Output Swing Under Raw Mode.

When we changed REG_0x1A[7:6]=1 and REG_0x0D[0]=0 to REG_0x1A[7:6]=3 and REG_0x0D[0]=0 in case of Retimed mode(CDR Enabled),

we confirmed 25G communication error decreased.

Are these register settings effective for Retimed mode(CDR Enabled) not Raw mode ?

Does these registers change the bandwidth or something other than changing the amplitude?

And

When we use Raw mode for 1G communication, could you please let us know if there are any registers that we should be careful about?

Thanks

Kenji Mizobuchi