Part Number: DP83869HM

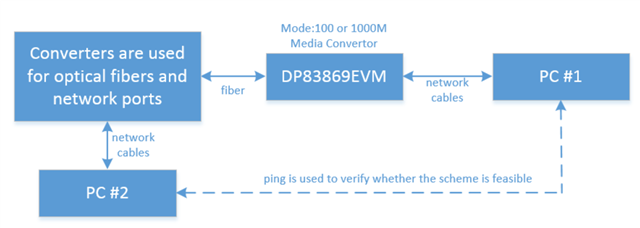

Other Parts Discussed in Thread: DP83869EVM

Hi team,

Using the MII interface of the STM32F407ZGT6 and the DP83869HM, the processor only supports 10/100M, so the initialization register configuration is as follows:

01DFH=0060H

0000H=3100H

0004H=01E1H

0009H=0000H

0010H=5048H

001FH=4000H

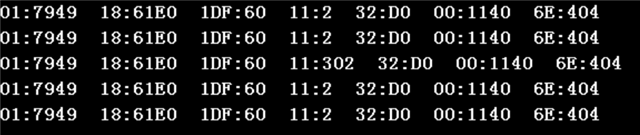

After the configuration is complete, the cycle reads some status register information as follows:

0001H=7949H

006EH=0400H

01DFH=0060H

0010H=5048H

0032H=00D0H

Plugging in and un-plugging the network cable does not reflect on the status register, what can be done to locate the cause of the problem?

The STM32F407ZGT6 and DP83848 have been used as MII and are working correctly.

The schematic is attached

Best Regards,

Amy