Hi

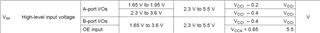

If the following two levelshifters' logic levels SPECs does not match with the main chip logic level.

Will there be any risks involved?

e.g.

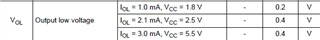

Vol 0.4 > VIL 0.15

main chip

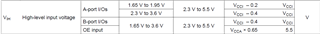

TXS0102DCUR

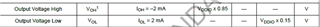

VOH VDDIO*0.85(2.805V) < VIH VCCI-0.4V(2.9V).

VOL VDDIO*0.15(0.495V) > VIL 0.15

VDDIO = VCCI = 3.3V

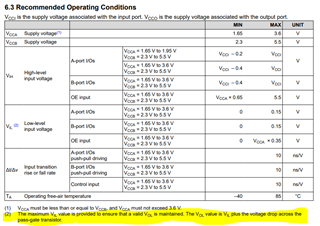

main chip

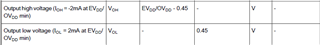

TXS0104EPWR

VOH EVDD-0.45V( 1.35V) > VCCI-0.2V( 1.6V)

VOL 0.45V > VIL 0.15V

main chip

TXS0104EPWR