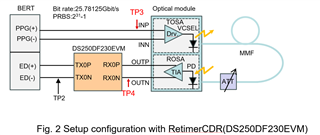

Part Number: DS250DF230EVM

Other Parts Discussed in Thread: SIGCONARCHITECT, DS250DF230

Using the DS250DF230EVM, I am trying to compare the BER performance of an optical module (DUT) currently under development with and without the RetimerCDR function.

Therefore, please answer the following questions.

(Question 1)

In this case, in order to switch with/without the RetimerCDR function in SigConArchitect, turn on/off the "Enable" button of "PRBS Generator Configurators" in the "PRBS Gen/Checkr" tab of "High Level Page". Should I do that?

Also, if the above method is incorrect, please let me know the correct method.

(Question 2)

When the “Enable” button of “PRBS Generator Configurators” is ON, is the Tx output data the same data that is regenerated by RetimerCDR based on the DUT output data?

Or is it completely new PRBS data that is generated by extracting only the clock based on the DUT output data (in other words, data that is completely different from the DUT output data)?

(Question 3)

Regarding Tx output data with CDR locked, what is the difference between turning on the "Enable" button in "PRBS Generator Configurators" and turning it off?

(This question may be similar to questions 1 and 2, but please answer.)

Thank you for your support.