Hi,

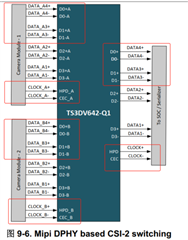

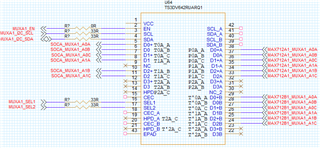

As you can see below figure,I add some red block which I want to use the two lane MIPI DPHY for ramera signal,

Would you please share some information for me:

1. Can this design work well, is there any risk should be paid attention?

2. Does this design used in any Mass Production without any problem before?

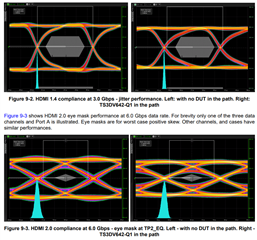

3. Does Ti team have any signal test report like the hdmi1.4 complicnace at 3Gbps and 6Gbps eye diagram before and after the mux shown in spec ?

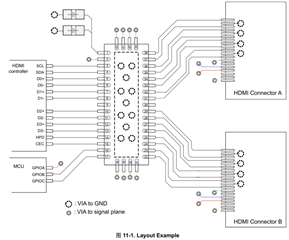

4. About the PCB route guide, do we take reference in figure 11-1?