Part Number: DS90UB941AS-Q1EVM

Other Parts Discussed in Thread: ALP

Hello,

We are trying to validate the DSI input with DS90UB941AS-Q1EVM. In our project we are using a Qualcomm SOC with Android. We adapt the output from DSI from SOC and placed in the input DSI connector from TI EVM.

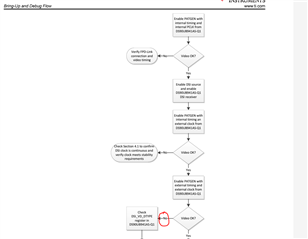

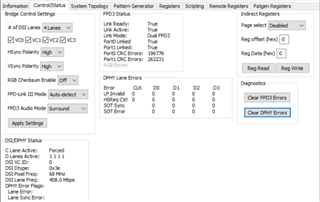

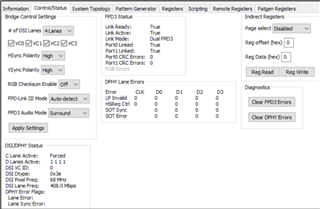

We are following the SNLA356 MIPI DSI Bring up guide.

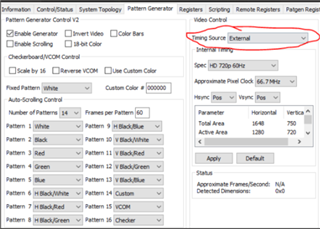

We are in this step in red. We configured the the mipi dsi clock as continuous and set to External Patgen, but we don´t have video.

We would like to know if you have some Android Parameters for DSI that we can setup for DSI TI EVM Input?

And Serializer Configuration?

,

,