Hello expert,

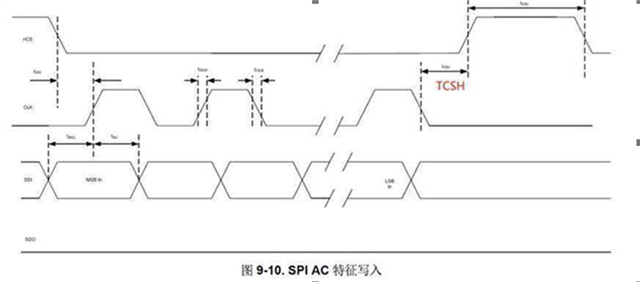

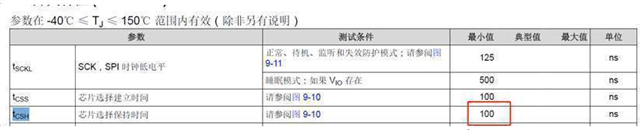

May I ask must the time difference (TCSH) between the failing edge of SPI CLK to the rising edge of nCS be kept in 100ns?

My customer uses F28P65(C2000)'s SPI to communicate with TCAN1146-Q1, while its the time difference SPICLK to nCS is just 3ns. My customer doesn't meet the communication issue now. However, we still check if there are any risks?

Best regards,

wenting