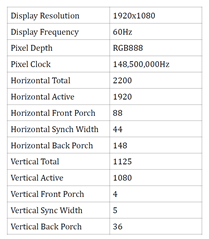

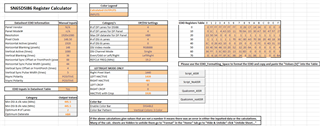

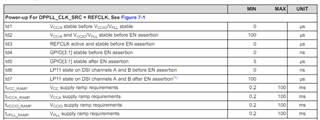

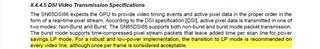

We have a Xilinx Artix-7 FPGA design that produces two 1920 x 1080 MIPI video streams. Each stream is routed through a Meticom MC20902 chip before going to the SN65DSI86 chip. We are using the TI spreadsheet to generate register settings for the SN65DSI86 and I've verified that the timing values in the registers are correct. We can see 3840x1080 Display Port video out of the SN65DSI86 on the external monitor when we enable the SN65DSI86 test pattern. However, we are unable to successfully transfer DSI video through the SN65DSI86. We are only operating in single channel mode until we get a functional DSI interface. The MIPI stream as been modeled, checked and appears to be in compliance with the SN65DSI86 datasheet, but we have struggled with this device for weeks without making progress. We are operating the MIPI interface with a Xilinx D-PHY IP core driven by a custom DSI interface containing provisions to synchronize the DSI to a video frame sync input. Is there a HDL behavioral model available to assist in determining what might be offending the SN65DSI86 DSI interface? Also, could you please direct us to a FAE operating out of the the San Diego region for assistant? Any other suggestions that might assist would be appreciated.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.