Part Number: TCAN1145-Q1

Other Parts Discussed in Thread: ESD2CAN24

Hi, Support Team

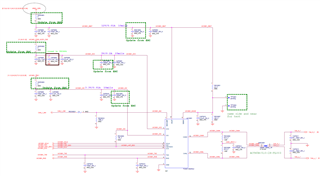

schematic as below chart: have any concern?

Q1: About TCAN1145A

- How to placement termination resistors? Follow EVB termination resistors near transceiver IC or datasheets chapter 13 “Layout” (near connector)?

- About SPI. Is only nINT/SDO need external pull-up 10k ohm (inner open drain)? Other pins can use internal pull-up resistors(~350 k ohm)? (Datasheet Figure 10-5. ;REVISED MARCH 2022)

- About INH pin, need external pull-down 100k ohm for inner PMOS open drain.

Q2: about WAKE pin

- I only can image, a mechanical if can provide voltage transition will trigger that device wake-up, right?

- The “WAKE” detection “H”(“L”) to “L”(“H”) (VHmin = Vsup-2V, VLmax = Vsup-3.5V) divider from Vsup.

- How to design “WAKE” pins parallel capacitor? Datasheet is 22nF. But EVM is 0.01uF. Which is better

if any suggestion, Please advise me.

Thanks,

Best regards,

Lawrence