Other Parts Discussed in Thread: DP83869

Hello,

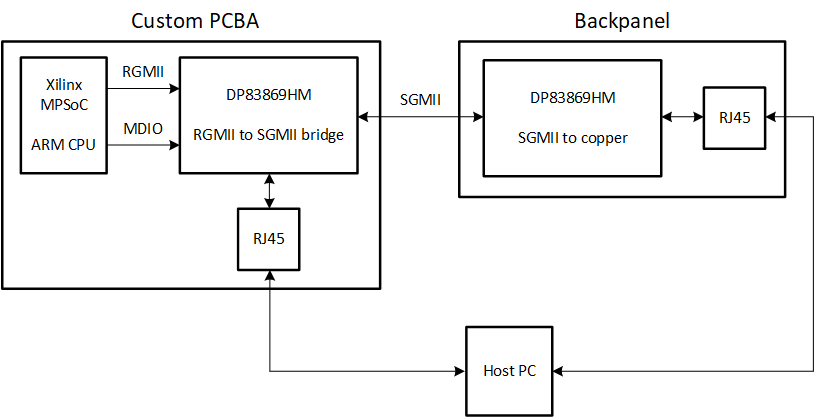

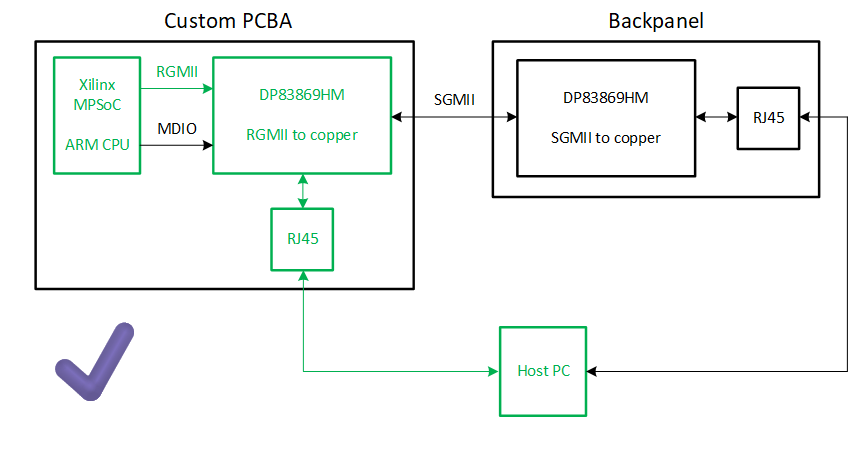

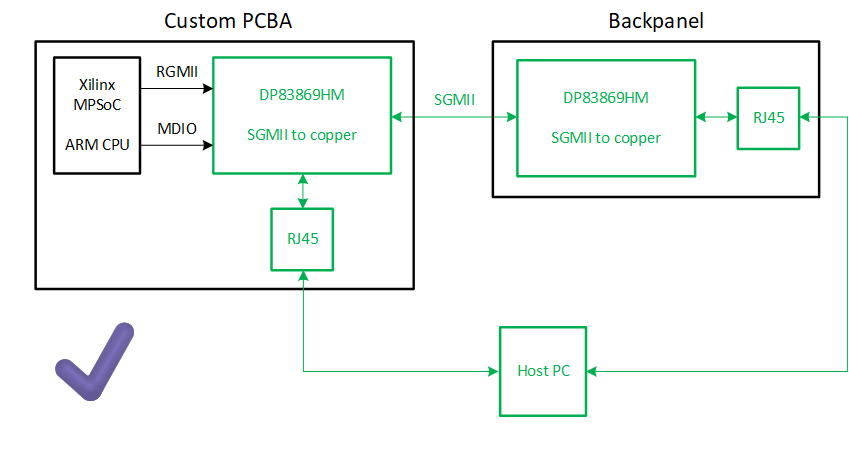

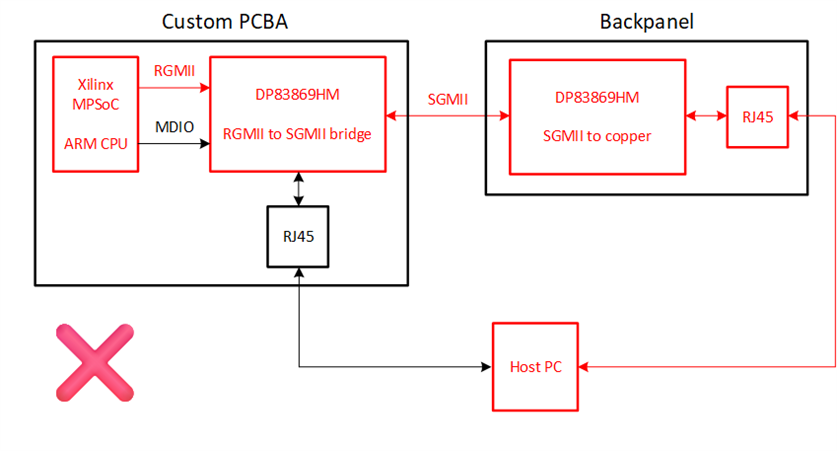

We have a set up with a custom PCBA and a backpanel, both containing an DP83869HM PHY chip. See this block diagram:

┌──────────────────────────────────────────┐ ┌──────────────────────────────┐ │ │ │ │ │ ┌──────────┐ ┌────────────────────┐ │ │ ┌───────────────┐ │ │ │ │RGMII │ │ │ │ │ │ ┌──────┐ │ │ │ Xilinx ├─────►│ DP83869HM │ │SGMII│ │ DP83869HM │ │ │ │ │ │ MPSoC │ │ ├─┼─────┤►│ ├──►│ RJ45 │ │ │ │ │MDIO │ │ │ │ │ │ │ │ │ │ │ ARM CPU ├─────►│RGMII to GMII bridge│ │ │ │SGMII to Copper│ └──────┘ │ │ │ │ │ │ │ │ │ │ │ │ └──────────┘ └────────────────────┘ │ │ └───────────────┘ │ │ Custom PCBA │ │ Backpanel │ └──────────────────────────────────────────┘ └──────────────────────────────┘

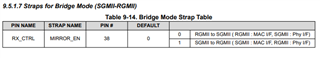

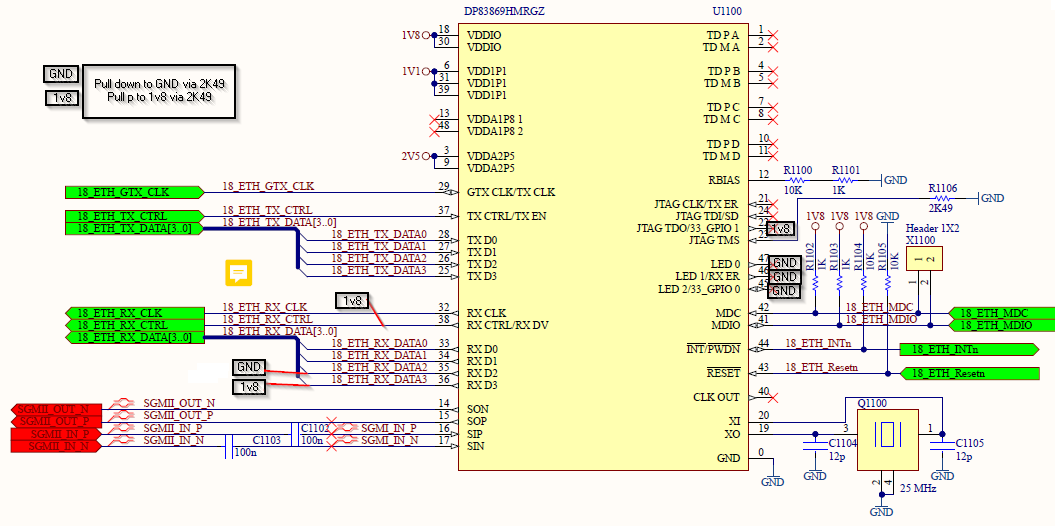

The PHY on the custom PCBA is connected to an ARM CPU (which is part of the Xilinx MPSoC) via MDIO and RGMII. The PHY on the backpanel is not connected to the CPU at all, so we cannot access it from the CPU, but it has been confirmed that it is working correctly. The PHY on the custom PCBA has strap resistors to work in RGMII-to-SGMII bridge mode, and the PHY on the backpanel has strap resistors to work in SGMII-to-Copper mode. We are running U-Boot on the CPU to configure the PHY.

When we try to send a packet from the ARM CPU to a host PC (connected to RJ45), it will only wait for auto negotiation to complete:

ethernet@ff0c0000 Waiting for PHY auto negotiation to complete........

Register 0x1 contains 0x7949, which indicates that auto negotiation has not yet completed. However, we see on the host PC that it has a successful link and it has finished auto negotiation. Register 0x6E contains 0x650, which indicates the boot strap registers have been configured for RGMII-to-SGMII bridge with MIRROR_EN disabled (which is required for the RGMII-to-SGMII bridge, if it was 1, then we would have a SGMII-to-RGMII bridge). However, when we read register 0x1DF, it shows the value 0x43, which has the bit BRIDGE_MODE_RGMII_MAC set to 1, indicating there is a SGMII-to-RGMII bridge. It seems there is a mistake in the datasheet, because section 9.4.8.4 describes we need to write 0x43 to the register to get an RGMII-to-SGMII bridge, but section 9.6.1.65 shows that BRIDGE_MODE_RGMII_MAC (the 4 in 0x43) has to be 0. Nevertheless, both modes are currently not working for us.

In the device driver of the PHY, we have disabled the part where it waits for auto negotiation (this if statement), and then when we set 0x1DF to 0x43, the ARM CPU reports that there is a link and when we disconnect the host PC from the RJ45 connector, it also reports there is no link anymore. However, when it does report that there is a link, we don't see any packets which are sent by the ARM CPU on the host PC. When we set 0x1DF to 0x3, it will only report that there is no link. We tried this because we are not sure if the PHY on the custom PCBA needs auto negotiation, because it seems this is already managed by the PHY on the backpanel.

In all of the described cases, the host PC shows a succesfull link.

Our device tree configurations look the following:&gem1 {

phy-mode = "rgmii-id";

phy-handle = <&phy0>;

status = "okay";

mdio: mdio@0 {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

reset-gpios = <&gpio 51 GPIO_ACTIVE_LOW>;

reset-assert-us = <100>;

reset-deassert-us = <280>;

phy0: ethernet-phy@05 {

#phy-cells = <1>;

status = "okay";

compatible = "ethernet-phy-ieee802.3-c45";

reg = <0x05>;

reset-gpios = <&gpio 51 GPIO_ACTIVE_LOW>;

reset-assert-us = <100>;

reset-deassert-us = <280>;

tx-fifo-depth = <0x1>;

rx-fifo-depth = <0x1>;

/* ti,op-mode = <0x03>; */

ti,max-output-impedance;

ti,clk-output-sel = <0x01>;

rx-internal-delay-ps = <2000>;

tx-internal-delay-ps = <2000>;

};

};

};

It seems that we have almost tried everything to get a successful link and auto negotiation, but it does not seem to work. What could we stiill be doing wrong?

Kind regards,

Roy Meijer