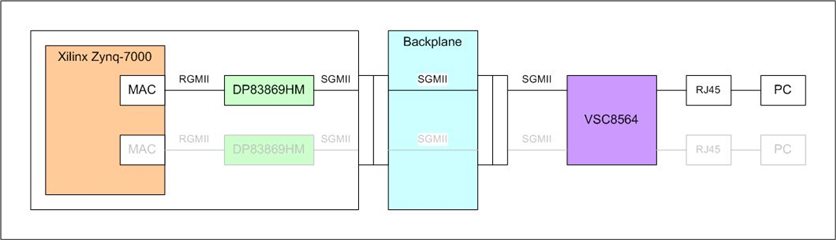

We are using a DP83869HM to bridge between RGMII and SGMII.

The RGMII side of the DP83869HM is connected to a Xilinx Zynq-7000 integrated MAC. The SGMII side is passing through a backplane to a board containing a VSC8564 (which is converting the SGMII to 1000BASE-T).

Two instances of this arrangement are implemented (see below) but a single one is currently being debugged (the other is greyed out below but its relevance is given later).

The VSC8564 is initialised first followed by the DP83869HM. The DP83869HM is configured into the desired mode with the strap configuration.

The register access sequence to the DP83869HM is shown below. The lines beginning BMCR are a print out of the most relevant registers.

Register accesses are described with some text and then what the access is, for example PHY_TI_CFG4 (ermw[0x0031] &= 0xFF7F) is an extended read-modify-write access to register 0x31, ANDing the value with 0xFF7F as the modification of the value read.

BMCR[0x0000]=0x0140 BMSR[0x0001]=0x794D SGMIIAnegStatus[0x0037]=0x0003 OPMODEdecode[0x01DF]=0x0043 FibreControl[0x0C00]=0x1140 FibreStatus[0x0C01]=0x617D

sw restart (rmw[0x001F] |= 0x4000)

MII reset (rmw[0x0000] |= 0x8000)

Delay

set PHY_CTRL (w[0x0010] 0x5048)

set RGMIIDCTL (ew[0x0086] 0x0077)

set RGMIICTL (ew[0x0032] 0x00D0)

SW workaround for unstable link when RX_CTRL is not STRAP MODE 3 or 4

PHY_TI_CFG4 (ermw[0x0031] &= 0xFF7F)

Aneg Adv (rmw[0x0031] |= 0x0DE0)

Aneg Adv (rmw[0x0009] |= 0x0300)

Aneg trigger (rmw[0x0000] |= 0x1200)

Waiting for PHY to complete autonegotiation.

BMCR[0x0000]=0x1140 BMSR[0x0001]=0x794D SGMIIAnegStatus[0x0037]=0x0003 OPMODEdecode[0x01DF]=0x0043 FibreControl[0x0C00]=0x1140 FibreStatus[0x0C01]=0x6179

BMCR[0x0000]=0x1140 BMSR[0x0001]=0x794D SGMIIAnegStatus[0x0037]=0x0001 OPMODEdecode[0x01DF]=0x0043 FibreControl[0x0C00]=0x1140 FibreStatus[0x0C01]=0x617D

The final two register state print-outs are one second apart and the last register states are repeatedly read the same for 30 further seconds with no change.

It can be seen that the link status is reported as Link up (BMSR bit 2) and Autonegotiation process is reported as not complete (BMSR bit 5) but no remote fault is indicated (BMSR bit 4).

However, the Fibre Status register also reports Link up (FibreStatus bit 2), but Autonegotiation process is reported as complete (FibreStatus bit 5) but with a remote fault indicated (FibreStatus bit 4).

It's not clear which one is relevant to RGMII-SGMII bridge mode but both indicate a problem. I'd appreciate some help in sorting out this issue.

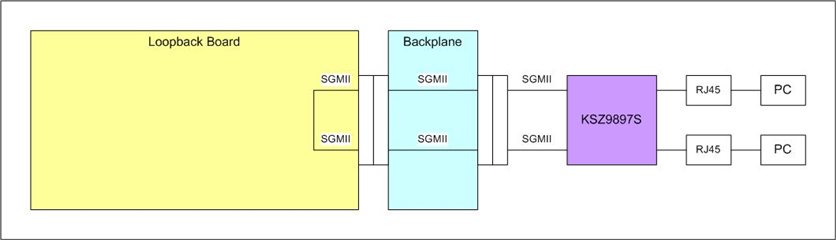

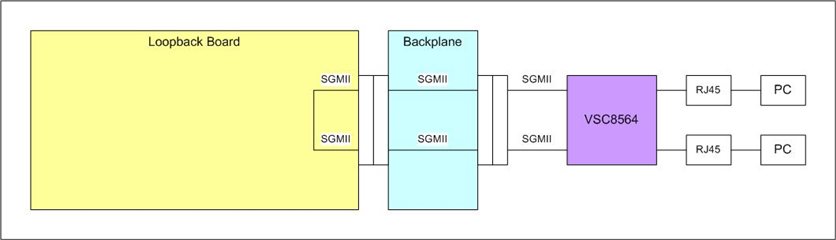

Background: The backplane/VSC8564/PC parts of the circuit have been tested with an SGMII loopback plugged into the backplane (as shown below). The SGMII links successfully autonegotiate to 1G and the two PC's can ping each other. Therefore, it is assumed that the SGMII links are OK in terms of PCB trace impedances/etc and also the VSC8564 setup is correct.