Part Number: TIC12400EVM-KIT

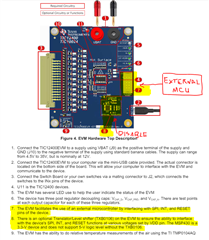

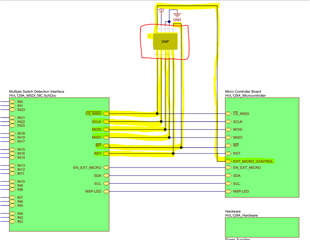

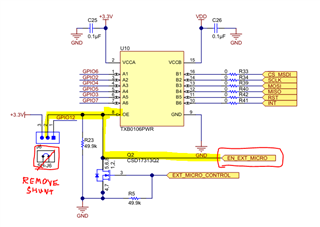

Other Parts Discussed in Thread: TIC12400, , TXB0106, TIC12400-Q1

I am using TIC12400 EVM KIT , in technical document its is mentioned that App Center and TIC12400 GUI App software to be used. But i am not getting this software. what to do?