I am trying to interface DP83867 with Jetson ORIN.

I see error as below

[ 20.163987] mdio_bus 2310000.ethernet: MDIO device at address 0 is missing. [ 20.172251] nvethernet 2310000.ethernet: failed to connect PHY [ 20.179193] net eth0: ether_open: Cannot attach to PHY (error: -19)

My DTS file update is as below

ethernet@2310000 {

status = "okay";

nvidia,mac-addr-idx = <0>;

nvidia,max-platform-mtu = <8000>;

nvidia,pause_frames = <0>;

local-mac-adress = [1a 2b 3c 4d 5e 6f];

nvidia,phy-reset-gpio = <&tegra_main_gpio TEGRA234_MAIN_GPIO(G, 5) 0>;

phy-handle = <&phy>;

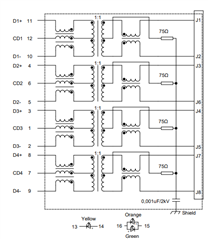

phy-mode = "rgmii-id";

mdio {

compatible = "nvidia,eqos-mdio";

#address-cells = <1>;

#size-cells = <0>;

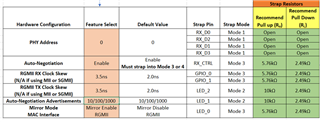

phy: phy@0 {

reg = <0>;

compatible = "ethernet-phy-ieee802.3-c22";

tx-fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

rx-fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

ti,max-output-impedance;

// ti,clk-output-sel = <DP83867_CLK_O_SEL_CHN_A_RCLK>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_25_NS>;

ti,tx-internal-delay = <DP83867_RGMIIDCTL_2_75_NS>;

interrupt-parent = <&tegra_main_gpio>;

interrupts = <TEGRA234_MAIN_GPIO(G, 4) IRQ_TYPE_LEVEL_LOW>; //<TODO> Need to check

};

};

};