Part Number: DS125DF1610

Hello E2E Experts,

Good day.

Reference E2E forum:

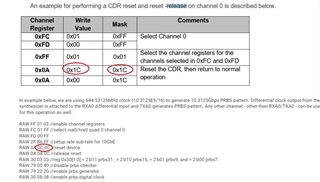

I looked at the CDR reset procedures in the programming guide and in one of your link on the forum. There are some differences and I would like to clarify them.

The procedure described in the programming manual (page 52) consists of:

RAW 0A 1C 1C // reset device

RAW 0A 00 1C // reset - release

That is, bits 2-4 of register 0x0A are first set to “1” and then reset to “0”.

The procedure described on the forum is different - the mask 0x0C is used, not 0x1C. That is, bit 4 of register 0x0A is not involved in the CDR-reset procedure.

Please tell me which option is correct.

P.S. I am attaching a screenshot with a description. Tell me please, do you see my screenshots? I don't see them in our correspondence.

Regards,

TI-CSC