Part Number: SN65DSI86

Hello:

Problem description: During the production process of the production line, MIPI to EDP screen did not display. After powering off and turning on again, there is still no display.

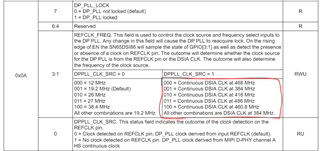

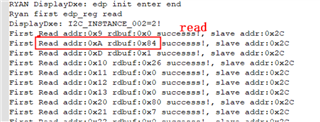

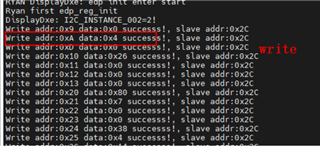

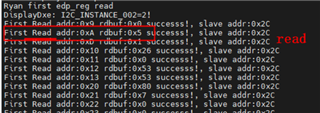

Problem analysis:

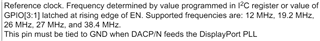

1. The power on timing of SN65DSI86ZXHR meets the requirements of the specifications.

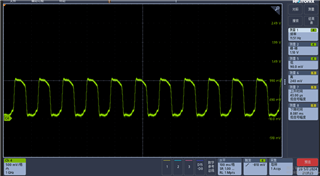

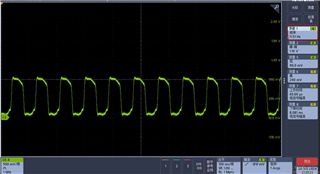

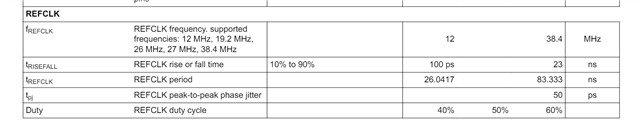

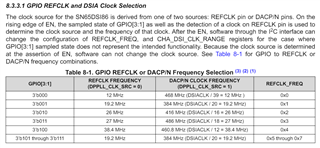

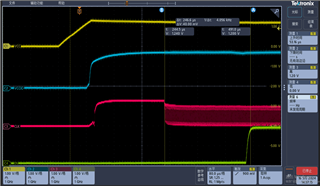

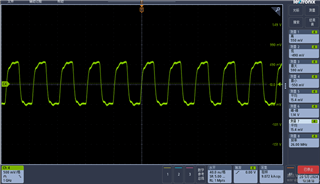

2. Measure the waveform of the external crystal oscillator at 26M. Does it meet the requirements? (Test DC, 1M Ω gear)

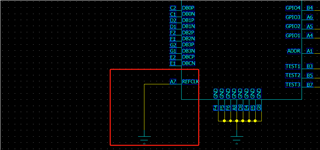

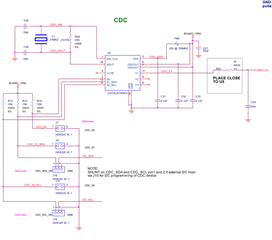

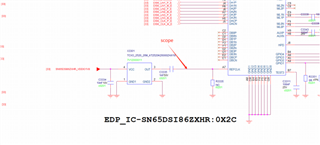

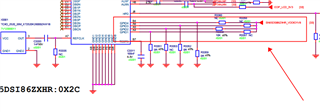

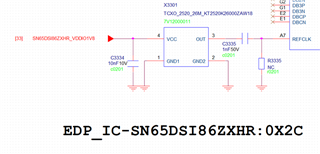

3. Design principle diagram of external clock

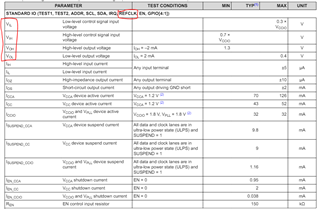

4. Crystal oscillator input, AC or DC. What is the minimum level that needs to be reached?

5. Signal waveform of C3335 replaced with 0 Ω resistance test