Part Number: DP83867E

Hi TI Team,

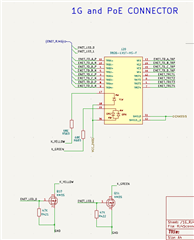

We're suing the DP83867ERGZT in a custom board application interfacing with ZYNQ FPGA MIOs on Gigabit Ethernet MAC(GEM3). This is the only device in the system and LEDs are driven through LED_0 and LED_1 pins. Is there any hardware strapping required for the chip to respond over MDI bus?

Protocol: RGMII

(default address should remain 0x00 is what I assume until any strapping is done)