Part Number: DP83869HM

Other Parts Discussed in Thread: TMS570LC4357, DP83640, HALCOGEN, DP83869

Tool/software:

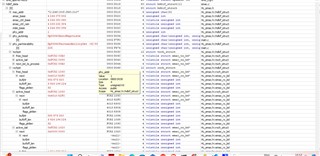

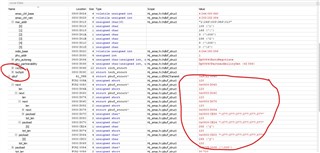

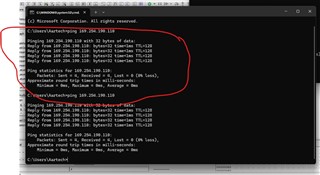

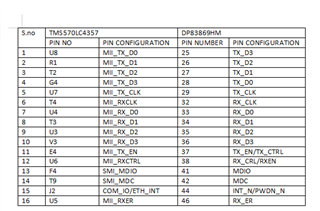

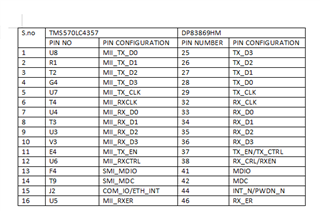

I am using TMS570lc4357 with dp82869 phy ic, and run loopback example, the phy is not responding,will you please what are the necessary registers I have to configure for tms570lc4357 emac and mdi eithdp83869 phy ic