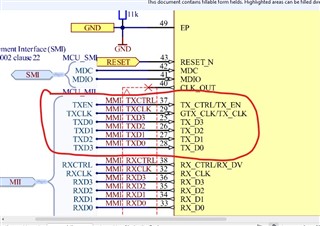

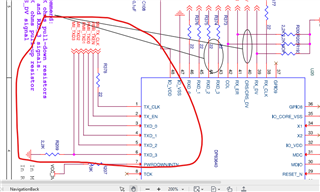

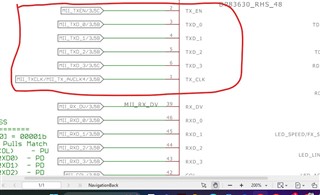

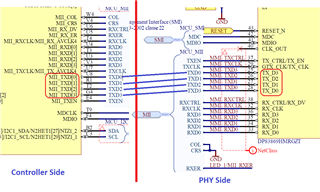

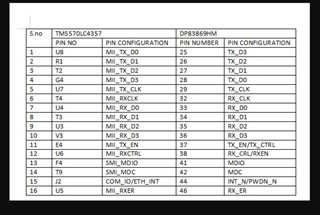

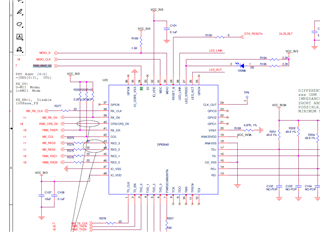

Part Number: TMS570LC4357

Other Parts Discussed in Thread: HALCOGEN, DP83869HM, DP83640, DP83869

Tool/software:

hii,

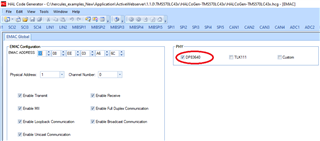

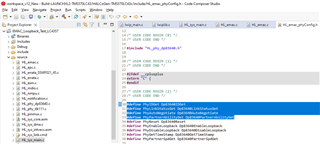

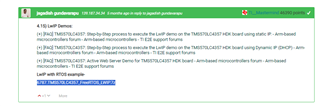

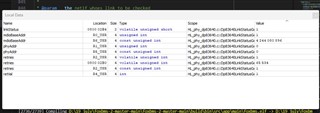

I am using tms570lc4357 with ethernet phy dp83869hm, i am not able to establish ethernet connectivity with tms, as halcogen is genrating drivers for 83860, please suggest solution to this

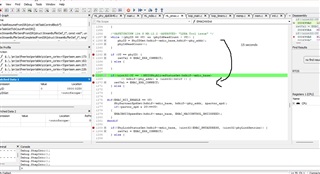

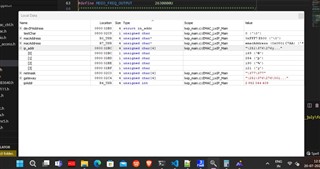

here it stucks for 12- 15 seconds

here it stucks for 12- 15 seconds

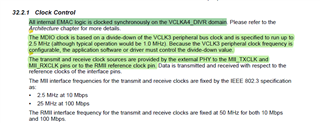

I change the mdc configuration,also i had given static ip, same result dp83640 also having same clock configurations,

I change the mdc configuration,also i had given static ip, same result dp83640 also having same clock configurations,

HERE WE STUCK DURING DHCP IP,

HERE WE STUCK DURING DHCP IP,

ABLE TO ASSIGN STATIC IP BUT NOT ABLE TO PING

ABLE TO ASSIGN STATIC IP BUT NOT ABLE TO PING