Part Number: DP83867IR

Tool/software:

Hi,

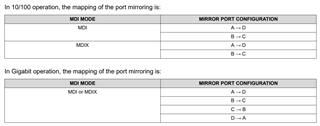

One question on LED_0 strap option. When I set it to mode 3, does that mean ports are mirrored internally or port mirror feature is enabled?

My hardware is able to connect to PC only in mode 3 but not in mode 1 (with no change in rest of the hardware/software). I have not swapped the ports in my PCB.

Best regards,

Bhagavath