Other Parts Discussed in Thread: AM5728

Tool/software:

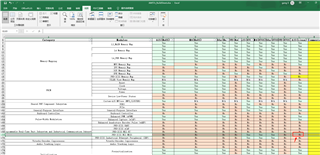

我目前在基于AM5728的开发板上使用了DP83848作为pru mii收发器,在系统启动中能正常识别到收发器。但是网口无法使用,通过ip addr命令看到网口状态一直为NO-CARRIER,state down,使用ifconfig命令分配ip地址后也无法通信,并且不能ping通自己。请协助检查一下pcb设计与设备树配置有无问题,给出解决问题的意见。原理图如下1121.Schematic Prints.pdf 设备树中相关配置

设备树中相关配置

/*

* Copyright (C) 2015-2016 Texas Instruments Incorporated - http://www.ti.com/

*

* This program is free software; you can redistribute it and/or modify

* it under the terms of the GNU General Public License version 2 as

* published by the Free Software Foundation.

*/

/ {

model = "TI AM5728 IDK";

//compatible = "ti,am572x-beagle-x15", "ti,am5728", "ti,dra742", "ti,dra74", "ti,dra7";

//compatible = "ti,am5728-idk", "ti,am5728", "ti,dra742", "ti,dra74",

// "ti,dra7";

aliases {

ethernet2 = &pruss2_emac0;

ethernet3 = &pruss2_emac1;

};

/* Dual-MAC Ethernet application node on PRU-ICSS2 */

pruss2_eth {

compatible = "ti,am57-prueth";

pruss = <&pruss2>;

sram = <&ocmcram1>;

interrupt-parent = <&pruss2_intc>;

pruss2_emac0: ethernet-mii0 {

phy-handle = <&pruss2_eth0_phy>;

phy-mode = "mii";

interrupts = <20>, <22>;

interrupt-names = "rx", "tx";

/* Filled in by bootloader */

local-mac-address = [00 00 00 00 00 00];

};

pruss2_emac1: ethernet-mii1 {

phy-handle = <&pruss2_eth1_phy>;

phy-mode = "mii";

interrupts = <21>, <23>;

interrupt-names = "rx", "tx";

/* Filled in by bootloader */

local-mac-address = [00 00 00 00 00 00];

};

};

};

&mac {

status = "okay";

dual_emac;

};

&cpsw_emac0 {

phy_id = <&davinci_mdio>, <1>;

phy-mode = "rgmii";

dual_emac_res_vlan = <1>;

};

&cpsw_emac1 {

phy_id = <&davinci_mdio>, <2>;

phy-mode = "rgmii";

dual_emac_res_vlan = <2>;

};

&gpio3 {

status = "okay";

};

&gpio5 {

status = "okay";

};

&pruss1 {

status = "disable";

pru1_0: pru0@4b234000 {

interrupt-parent = <&pruss1_intc>;

interrupts = <16>, <17>;

interrupt-names = "vring", "kick";

status = "okay";

};

pru1_1: pru1@4b238000 {

interrupt-parent = <&pruss1_intc>;

interrupts = <18>, <19>;

interrupt-names = "vring", "kick";

status = "okay";

};

};

&pruss2 {

status = "okay";

pru2_0: pru0@4b2b4000 {

interrupt-parent = <&pruss2_intc>;

interrupts = <16>, <17>;

interrupt-names = "vring", "kick";

status = "okay";

};

pru2_1: pru1@4b2b8000 {

interrupt-parent = <&pruss2_intc>;

interrupts = <18>, <19>;

interrupt-names = "vring", "kick";

status = "okay";

};

};

&pruss2_mdio {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&pru2_mii_pins_default>;

pruss2_eth0_phy: ethernet-phy@0 {

reg = <1>;

interrupt-parent = <&gpio3>;

interrupts = <26 IRQ_TYPE_EDGE_FALLING>;

};

pruss2_eth1_phy: ethernet-phy@1 {

reg = <3>;

interrupt-parent = <&gpio5>;

interrupts = <17 IRQ_TYPE_EDGE_FALLING>;

};

};

&pruss2_mdio {

reset-gpios = <&gpio7 10 GPIO_ACTIVE_LOW>,

<&gpio3 25 GPIO_ACTIVE_LOW>;

reset-delay-us = <2>; /* PHY datasheet states 1uS min */

};

&dra7_pmx_core {

gpio3_pins: gpio3_pins {

pinctrl-single,pins = <

DRA7XX_CORE_IOPAD(0x3548, (PIN_OUTPUT_PULLUP | MUX_MODE14)) /* vin1a_d21.gpio3_25 */

DRA7XX_CORE_IOPAD(0x354c, PIN_INPUT_PULLUP | MUX_MODE14) /* vin1a_d22.gpio3_26 */

>;

};

gpio5_pins: gpio5_pins {

pinctrl-single,pins = <

DRA7XX_CORE_IOPAD(0x3644, (PIN_INPUT_PULLUP | MUX_MODE14)) /* RMII_MHZ_50_CLK.gpio5_17 */

>;

};

gpio7_pins: gpio7_pins {

pinctrl-single,pins = <

DRA7XX_CORE_IOPAD(0x37b0, (PIN_OUTPUT_PULLUP | MUX_MODE14)) /* spi1_cs0.gpio7_10 (A24) */

>;

};

pru2_mii_pins_default: pru2_mii_pins_default {

pinctrl-single,pins = <

DRA7XX_CORE_IOPAD(0x36b8, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp1_axr1.pr2_mii_mt_clk */

DRA7XX_CORE_IOPAD(0x36d4, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp1_axr8.pr2_mii0_txen */

DRA7XX_CORE_IOPAD(0x36e4, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp1_axr12.pr2_mii0_txd0 */

DRA7XX_CORE_IOPAD(0x36e0, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp1_axr11.pr2_mii0_txd1 */

DRA7XX_CORE_IOPAD(0x36dc, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp1_axr10.pr2_mii0_txd2 */

DRA7XX_CORE_IOPAD(0x36d8, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp1_axr9.pr2_mii0_txd3 */

DRA7XX_CORE_IOPAD(0x36e8, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp1_axr13.pr2_mii_mr0_clk */

DRA7XX_CORE_IOPAD(0x36ec, (PIN_INPUT_PULLDOWN | SLEWCONTROL | MUX_MODE11)) /* mcasp1_axr14.pr2_mii0_rxdv */

DRA7XX_CORE_IOPAD(0x36b4, (PIN_INPUT_PULLUP | SLEWCONTROL | MUX_MODE11)) /* mcasp1_axr0.pr2_mii0_rxer */

DRA7XX_CORE_IOPAD(0x370c, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp2_axr2.pr2_mii0_rxd0 */

DRA7XX_CORE_IOPAD(0x36f8, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp2_fsx.pr2_mii0_rxd1 */

DRA7XX_CORE_IOPAD(0x36f4, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp2_aclkx.pr2_mii0_rxd2 */

DRA7XX_CORE_IOPAD(0x36f0, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp1_axr15.pr2_mii0_rxd3 */

DRA7XX_CORE_IOPAD(0x3724, (PIN_INPUT_PULLDOWN | MUX_MODE11)) /* mcasp3_aclkx.pr2_mii0_crs */

DRA7XX_CORE_IOPAD(0x3728, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp3_fsx.pr2_mii0_col */

//DRA7XX_CORE_IOPAD(0x3710, (PIN_INPUT_PULLDOWN | SLEWCONTROL | MUX_MODE11)) /* mcasp2_axr3.pr2_mii0_rxlink */

DRA7XX_CORE_IOPAD(0x3774, (PIN_INPUT_PULLUP | MUX_MODE11)) /* gpio6_10.pr2_mii_mt1_clk */

DRA7XX_CORE_IOPAD(0x3778, (PIN_INPUT_PULLUP | MUX_MODE11)) /* gpio6_11.pr2_mii1_txen */

DRA7XX_CORE_IOPAD(0x3788, (PIN_INPUT_PULLUP | MUX_MODE11)) /* mmc3_dat1.pr2_mii1_txd0 */

DRA7XX_CORE_IOPAD(0x3784, (PIN_INPUT_PULLUP | MUX_MODE11)) /* mmc3_dat0.pr2_mii1_txd1 */

DRA7XX_CORE_IOPAD(0x3780, (PIN_INPUT_PULLUP | MUX_MODE11)) /* mmc3_cmd.pr2_mii1_txd2 */

DRA7XX_CORE_IOPAD(0x377c, (PIN_INPUT_PULLUP | MUX_MODE11)) /* mmc3_clk.pr2_mii1_txd3 */

DRA7XX_CORE_IOPAD(0x378c, (PIN_INPUT_PULLUP | MUX_MODE11)) /* mmc3_dat2 .pr2_mii_mr1_clk */

DRA7XX_CORE_IOPAD(0x3790, (PIN_INPUT_PULLDOWN | MUX_MODE11)) /* mmc3_dat3.pr2_mii1_rxdv */

DRA7XX_CORE_IOPAD(0x372c, (PIN_INPUT_PULLUP | SLEWCONTROL | MUX_MODE11)) /* mcasp3_axr0.pr2_mii1_rxer */

DRA7XX_CORE_IOPAD(0x37a0, (PIN_INPUT_PULLDOWN | MUX_MODE11)) /* mmc3_dat7.pr2_mii1_rxd0 */

DRA7XX_CORE_IOPAD(0x379c, (PIN_INPUT_PULLDOWN | MUX_MODE11)) /* mmc3_dat6.pr2_mii1_rxd1 */

DRA7XX_CORE_IOPAD(0x3798, (PIN_INPUT_PULLDOWN | MUX_MODE11)) /* mmc3_dat5.pr2_mii1_rxd2 */

DRA7XX_CORE_IOPAD(0x3794, (PIN_INPUT_PULLDOWN | MUX_MODE11)) /* mmc3_dat4.pr2_mii1_rxd3 */

DRA7XX_CORE_IOPAD(0x3698, (PIN_INPUT_PULLDOWN | MUX_MODE11)) /* xref_clk1.pr2_mii1_crs */

DRA7XX_CORE_IOPAD(0x3694, (PIN_INPUT_PULLDOWN | MUX_MODE11)) /* xref_clk0.pr2_mii1_col */

//DRA7XX_CORE_IOPAD(0x3730, (PIN_INPUT_PULLUP | SLEWCONTROL | MUX_MODE11)) /* mcasp3_axr1.pr2_mii1_rxlink */

DRA7XX_CORE_IOPAD(0x36a4, (PIN_INPUT_PULLDOWN | MUX_MODE11)) /* mcasp1_aclkx.pr2_mdio_mdclk */

DRA7XX_CORE_IOPAD(0x36a8, (PIN_INPUT_SLEW | MUX_MODE11)) /* mcasp1_fsx.pr2_mdio_data */

>;

};

};