Tool/software:

Hi,

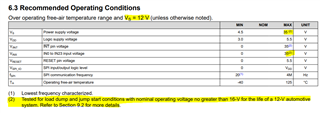

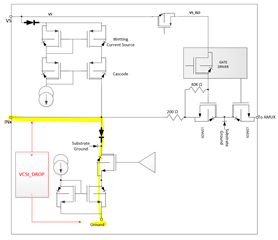

We are using TIC12400-Q1 MSDI through SPI for one of our products on iMX8 running on Linux 6.6. We have referred datasheet and tried to configure registers

through spidev interface. But we are observing that some registers are configured succesfully but some are failing. When a write and then

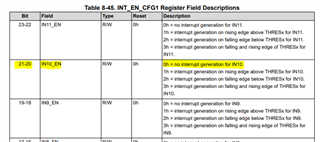

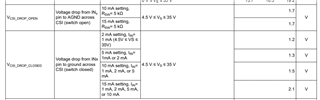

read is performed on the same register, we get different values. This is observed for some of registers only. For example, when THRES_COMP register is

configured for 4V for all inputs.

Write -

root@imx8mp-falcon:~# spidev_test -v -D /dev/spidev2.0 -H 0 -b 32 -p "\xFE\x1F\x00\xA2"

[14336.987180] setup mode 1, cs_high, 32 bits/w, 1000000 Hz max --> 0

[14337.004606] setup mode 1, cs_high, 32 bits/w, 1000000 Hz max --> 0

[14337.022013] setup mode 1, cs_high, 32 bits/w, 500000 Hz max --> 0

spi mode: 0x1

bits per word: 32

max speed: 500000 Hz (500 kHz)

TX | FE 1F 00 A2 __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ |....|

RX | 01 00 00 22 __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ |..."|

Read -

root@imx8mp-falcon:~# spidev_test -v -D /dev/spidev2.0 -H 0 -b 32 -p "\x00\x00\x00\x22"

[14483.315089] setup mode 1, cs_high, 32 bits/w, 1000000 Hz max --> 0

[14483.332530] setup mode 1, cs_high, 32 bits/w, 1000000 Hz max --> 0

[14483.349950] setup mode 1, cs_high, 32 bits/w, 500000 Hz max --> 0

spi mode: 0x1

bits per word: 32

max speed: 500000 Hz (500 kHz)

TX | 00 00 00 22 __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ |..."|

RX | 01 00 00 22 __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ |..."|

But some of register write like CS_SELECT (0x1C), Mode (0x32), Device Id (0x1) are success.

So can you pls inform what can be possibel reason here. Let me know if you need more info.

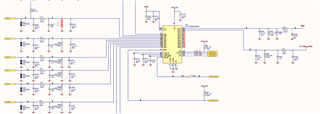

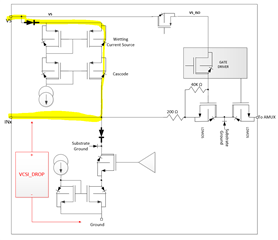

Attaching screenshot of the circuit here.