Tool/software:

Hello,BCI.docx

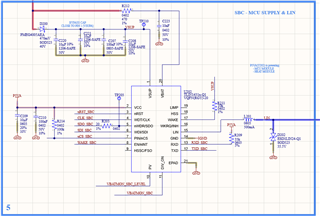

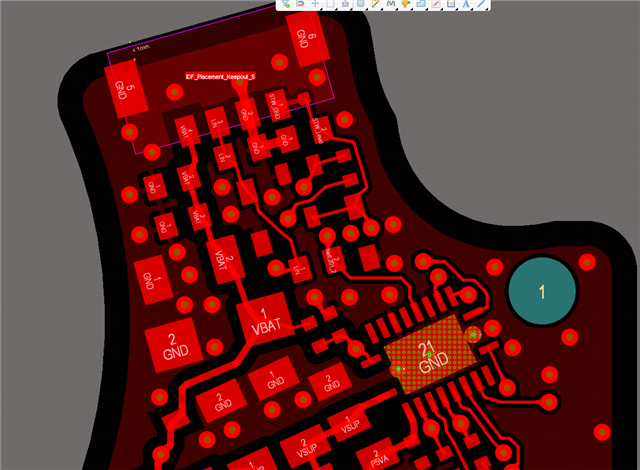

I am currently used TLIN14315 in an automotive project.

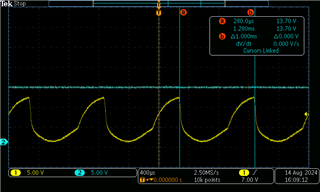

We have performed BCI (bulk current injection ) tests.

Short document for BCI test included in the documents .

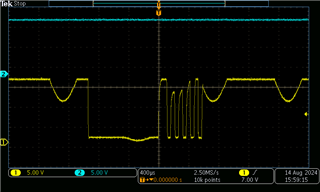

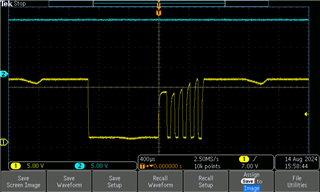

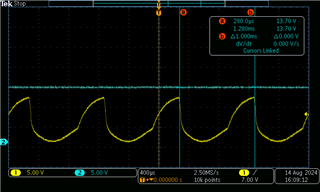

In the BCI (Bulk current injection) test we have an interesting behavior of the LIN driver.

When the LIN line is disconnected from the master during BCI test the inside low side MOS transistor from TL14315 start conducting because of the signal from the drain(our presumption).

When the LIN is connected with the master we have communication timeouts

Could you help us to understand the this behavior and possible ways of solving ?

Thank you

Marian