Tool/software:

Hi TI team,

[Example reference: TI p/n: TPD1E6B06DPLR; Package: DFN-0603 (X2SON); [Dimension:0.60 mm × 0.30 mm × 0.30 mm]:

I would like to enquire some information regarding "Chip-Scale Package" for our internal assembly process optimization.

(1) Do you have any similar IC product with "Chip-Scale Package", DFN-0603 & IC dimension of 0.60 mm × 0.30 mm × 0.30 mm? Need help to advise the MPN examples.

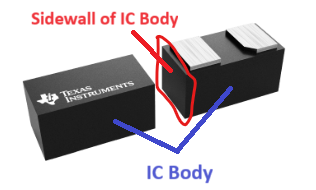

(2) As per IC picture below(IC geometry as example), for chip-scale package, the IC body (including sidewall) is by "Silicon Die". Is there any lamination/coating/protective layer at the silicon die(IC body)? What is the composition of the IC body?

(3) For this type of "Chip-Scale Package", if PCB solder is in-contact with the silicon die (sidewall of IC body as red-circled at IC picture), is there a risk that it may cause current leakage over lifetime (sidewall leakage)? Is this "sidewall leakage" risk common for wafer level chip scale package or any other related package technology?

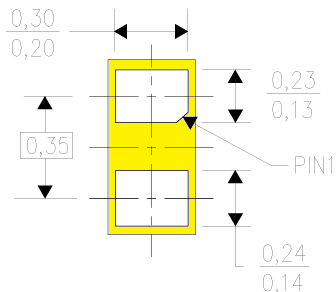

(4) For IC bottom (as per below picture-yellow color), is the yellow area conductive? Any protective layer/coating at this yellow area? What is the composition of the coating layer?

(5) Where I can find the application note regarding PCB pad stack design and stencil recommendation for this "Chip-Scale Package" (DFN-0603 with Silicon Die as IC body and similar package 0.60 mm × 0.30 mm)?

Thanks in advance.