Tool/software:

Hi Sir,

What is different between enable or disable AN signal bypass ?

If disable AN signal bypass , Does the Ethernet device (NIC or switch) also disable AN function ?

What setting do you recommend ?

thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Sir,

What is different between enable or disable AN signal bypass ?

If disable AN signal bypass , Does the Ethernet device (NIC or switch) also disable AN function ?

What setting do you recommend ?

thanks.

Hi Kevin,

Enabling the AN signal bypass allows DS560DF810 to send raw (non-retimed) data through the device when a signal is detected. This is important as AN data is 312.5 Mbps, which the retimer is unable to lock to.

Disabling AN signal bypass on the retimer does not directly disable it on connected NICs or switches. I would recommend enabling AN signal bypass if you expect to receive auto-negotiation signals. If you do not expect to receive these signals, then you could disable AN signal bypass.

How is your system bring up going with the retimer?

Thanks,

Drew

Hi Miller,

We found that sometimes NIC to Switch through retimer linkup success time was too longer than NIC to Switch directly when hot plug DAC cable. The connection may even fail need to re-plug DAC cable. If connection normal, the function and signal quality is always fine.

So , we suspect it maybe is device auto negotiation problem.

thanks.

Hi Kevin,

It's possible that AN is causing this.

You might also find it valuable to read back channel information from DS560DF810. You can look at heartbeat count to see how many CDR lock attempts have been made.

Thanks,

Drew

Hi Kevin,

You also mentioned that if the connection is normal, the function/signal quality is fine.

Can you add more details to this? What do you mean by a "normal" connection? Is this hot plugging optical modules?

What sort of linkup time are you seeing?

Thanks,

Drew

Hi Miller,

What do you mean by a "normal" connection? Is this hot plugging optical modules?

> The throughput is fine (50Gb/s) if CDR Lock and we used DAC cable.

What sort of linkup time are you seeing?

> About 5 Min , or CDR always can not lock.

1. If we set AN signal bypass =1 (default =0) , any side effect will happen ?

2. How to set different TX FFE coefficient independently for different channels in EEprom Mode ?

thanks.

Hi Kevin,

Which gearbox mode are you using? I assume you're using either 0x00 or 0x80. Can you try whichever mode you are not using?

Also, do you have an I2C controller that can be used to interface with the device? For debug, it may be valuable to try configuring the device with I2C controller instead of EEPROM. There are patches that are implemented with I2C controller that are not implemented via EEPROM.

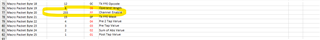

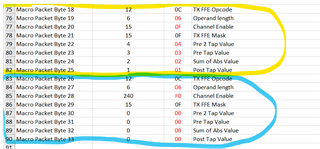

To adjust TX FFE coefficient independently, you will need to have this "macro packet" multiple times in EEPROM. To select the channels, modify the channel enable data. The channel enable is bit mapped to the channels. In other words, bit 0 selects channel 0, bit 7 selects channel 7. To modify channels 0 and 1, use channel enable = 0x03.

Thanks,

Drew

Hi Miller,

I assume you're using either 0x00 or 0x80. Can you try whichever mode you are not using?

-> We default uesd 0x00: Straight connection , and what different between 0x00: Straight connection and 0x80: Analog low latency path ?

do you have an I2C controller that can be used to interface with the device?

-> Our system do not have I2c master controller, but I have Ti i2c master dongle +TI-DS560-Latte for debug.

To adjust TX FFE coefficient independently, you will need to have this "macro packet" multiple times in EEPROM

-> I still do not understand "macro packet" multiple times means and how to program it , could you provide example file (like EEPROM_ConfigUpdatedSingle) for our reference ?

thanks.

Hi Kevin,

We default used 0x00: Straight connection , and what different between 0x00: Straight connection and 0x80: Analog low latency path ?

-> The primary difference is that straight mode 0x00 goes through a SERDES functional block, while analog low latency mode 0x80 does not go through this functional block. These modes are functionally similar, but have some different internal digital configuration. Because of this, I believe it would be valuable for you to try analog low latency mode (0x80) to see if you observe the same issue.

Our system do not have I2c master controller, but I have Ti i2c master dongle +TI-DS560-Latte for debug.

-> Depending on the results from the analog low latency mode test, I think it may be valuable to try configuring the device through the API using an I2C master controller in order to determine if the behavior you're observing is due to EEPROM configuration.

I still do not understand "macro packet" multiple times means and how to program it , could you provide example file (like EEPROM_ConfigUpdatedSingle) for our reference ?

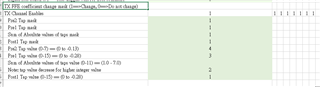

-> A macro packet consists of an opcode, the number of operands, and then the associate operands. For the TX FFE macro, this consists of the opcode (0x0C), the number of operands (6), then the operands (channel enable mask, tx ffe mask, pre 2 value, pre 1 value, main value, post 1 value).

I've attached an example file. In this file, I just manually set TX FFE values in the EEPROM_810 section. Note that in the attached file, the first TX FFE macro packet configures channels 0-3, and the second TX FFE macro packet configures channels 4-7.

EEPROM_ConfigUpdatedSingle_Manual_TX_FFE.xlsx

Thanks,

Drew

Hi Miller,

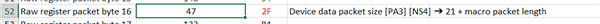

Thank for your example file. Does "Paket length " need to change If Macro Packet Byte increased quantity?

thanks.

Hi Kevin,

Yes good catch, the packet length will need to be increased. Note that increasing packet length should also automatically increase the value in the "device data packet size" cell too.

Please let us know how testing with 0x80 mode goes.

Thanks,

Drew

Hi Kevin,

I wanted to kindly follow up on this. Are there any updates from your side? Are you still debugging issues with hot plugging?

Thanks,

Drew

Hi Miller,

The issue seems have solved currently, we are waiting for more system to verify.

Thank for your support.

Hi Kevin,

Thanks for the update. Glad to hear that the issue appears to be resolved!

Are there any changes you made on your side to resolve this issue?

Thanks,

Drew

Hi Miller,

We change to AN signal bypass =1 and analog low latency mode (0x80) .

thanks.