Part Number: TDES954

Other Parts Discussed in Thread: TSER953

Tool/software:

Dear TI,

Please kindly send information about how to interpret the D3 register status based on the EQ levels.

Thanks,

Abel

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Abel,

Please see the following E2E which applies to the TDES954: https://e2e.ti.com/support/interface-group/interface/f/interface-forum/953827/ds90ub936-q1-aeq_status-register-0xd3-clarification

Pleaser use the following Application Note as a reference as well on AEQ: https://www.ti.com/lit/an/snla301/snla301.pdf?ts=1727364189692&ref_url=https%253A%252F%252Fwww.google.com%252F

Best,

Zoe

Hi Zoe,

Thanks for reply.

I did few tests using MAP and different FAKRA cables , here is one plot for a 5m cable using customs boards , TDES954 - TSER953

Did 3 interations, is this valid? Can I use MAP directly to validate the cable quality ? Or I have to create my own plots by manual check registers in the firmware?

Thank you,

Abel

Hi Abel,

To validate the cable quality and the system, we would recommend taking S-parameter measurements for the TSER and TDES PCBs, and the cable. This will confirm if the total channel requirements are met across the entire operating frequency range of the V3Link devices. MAP results may change dependent on the operating environment. Overall, MAP will show if specific strobe position and EQ settings can be found without an error criteria being met and lock is stable during the dwell time.

Best,

Zoe

Hi Abel,

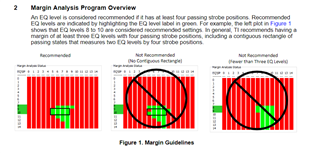

These plots would be considered passing. The criteria for what is considered "passing" is shown below from FPD-Link Margin Analysis Program (MAP) user's guide (SNLU243):

Best,

Zoe