Part Number: DP83825I

Tool/software:

We are using TI DP83825I Ethernet Phy in RMII Slave configuration with Ambarella CV25 SOC running Linux Kernel 5.4.

We were able to make the Ethernet work in RMII Master mode with the following device tree bindings configuration. The pinctrls, power and reset gpios are configured correctly according to the board.

DTSI:

mac0: ethernet@e000e000 {

compatible = "ambarella,eth";

#address-cells = <1>;

#size-cells = <0>;

reg = <0xe000e000 0x2000>;

interrupts = <0 58 0x4>;

pinctrl-names = "default";

pinctrl-0 = <&rmii_pins>;

phy-mode = "rmii";

amb,rct-regmap = <&rct_syscon>;

amb,scr-regmap = <&scratchpad_syscon>;

amb,tx-ring-size = <32>;

amb,rx-ring-size = <64>;

amb,ipc-tx;

amb,ipc-rx;

amb,enhance;

amb,ahb-12mhz-div = <5>;

clock-names = "ptp_ref";

clocks= <&osc>;

};

DTS:

mac0: ethernet@e000e000 {

status = "ok";

pinctrl-0 = <&rmii_pins &enet_2nd_ref_clk_pins_a>;

phy-mode = "rmii";

amb,tx-clk-invert;

phy@0 {

reg = <0>;

pwr-gpios = <&gpio 94 0x1>;

rst-gpios = <&gpio 35 0x0>;

txen-skew-ps = <0>;

rxdv-skew-ps = <0>;

rxd0-skew-ps = <0>;

rxd1-skew-ps = <0>;

rxd2-skew-ps = <0>;

rxd3-skew-ps = <0>;

txd0-skew-ps = <0>;

txd1-skew-ps = <0>;

txd2-skew-ps = <0>;

txd3-skew-ps = <0>;

};

};

We are not able to make the Ethernet work in RMII Slave Mode, "eth0" interface is up with IP Address but ping is not working.

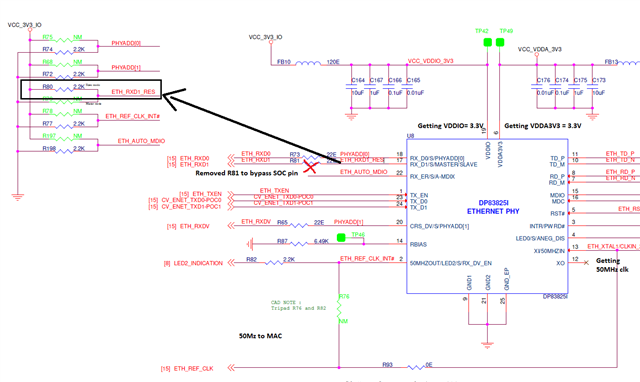

We have set "RX_D1" as "1" for DP83825I from hardware configuration. We have made sure the 50 MHz clock is given to the TI DP83825I PHY for slave operation. Also the same 50 MHz clock is given to the MAC.

We are getting the following output of ifconfig, ethtool and ip commands when configured in slave mode.

# ifconfig

eth0 Link encap:Ethernet HWaddr 2E:35:35:4D:41:BF

inet addr:192.168.1.250 Bcast:192.168.1.255 Mask:255.255.255.0

UP BROADCAST MULTICAST MTU:1500 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:0 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)

Interrupt:28

lo Link encap:Local Loopback

inet addr:127.0.0.1 Mask:255.0.0.0

UP LOOPBACK RUNNING MTU:65536 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:0 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)

# ethtool eth0

Settings for eth0:

Supported ports: [ TP MII ]

Supported link modes: Not reported

Supported pause frame use: Symmetric Receive-only

Supports auto-negotiation: No

Advertised link modes: Not reported

Advertised pause frame use: No

Advertised auto-negotiation: No

Speed: 10Mb/s

Duplex: Half

Port: MII

PHYAD: 0

Transceiver: internal

Auto-negotiation: off

Current message level: 0x00000001 (1)

drv

Link detected: no

# ip a

1: lo: <LOOPBACK,UP,LOWER_UP> mtu 65536 qdisc noqueue qlen 1000

link/loopback 00:00:00:00:00:00 brd 00:00:00:00:00:00

inet 127.0.0.1/8 scope host lo

valid_lft forever preferred_lft forever

2: eth0: <NO-CARRIER,BROADCAST,MULTICAST,UP> mtu 1500 qdisc pfifo_fast qlen 1000

link/ether 2e:35:35:4d:41:bf brd ff:ff:ff:ff:ff:ff

inet 192.168.1.250/24 brd 192.168.1.255 scope global noprefixroute eth0

valid_lft forever preferred_lft forever

Loopback ping is working in slave mode:

# ping 127.0.0.1

PING 127.0.0.1 (127.0.0.1): 56 data bytes

64 bytes from 127.0.0.1: seq=0 ttl=64 time=0.132 ms

64 bytes from 127.0.0.1: seq=1 ttl=64 time=0.049 ms

Can you please tell what DTSI/DTS changes from software need to be done for RMII Slave Mode operation?