Tool/software:

Hi,

I have a question about the DP83825I Ethernet PHY and the behaviour of its RST_N pin.

We are using the DP83825I in our design with a 1.8V VDDIO. However, we noticed that the RESET signal connected to the RST_N pin has a voltage level of 2.2V-2.5V instead of 1.8V.

According to the DP83825I datasheet, the RST_N pin should operate at the same voltage level as VDDIO. Could you please clarify the following

- Is the internal pull-up resistor on the RST_N pin fixed at 3.3V or is it connected to VDDIO as stated in the datasheet?

- If it is connected to VDDIO, are there any conditions under which this discrepancy could occur?

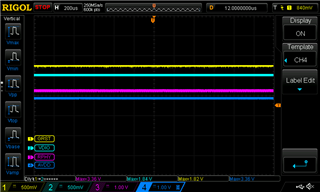

This behaviour is a key concern in our design, and resolving it is crucial to ensure proper operation. To help you understand the situation, I’ve attached two figures:

- One showing the behaviour with the PHY connected.

- The other shows the behaviour when the signal to the RST_N pin is disconnected.

Your advice on this matter would be greatly appreciated.

Thank you for your support!